## (11) **EP 1 874 986 B1**

(12)

## **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent: 23.01.2013 Bulletin 2013/04

(21) Application number: 06733343.5

(22) Date of filing: 25.04.2006

(51) Int Cl.:

C01B 31/02 (2006.01)

D01F 9/08 (2006.01)

C23C 16/04 (2006.01)

H01J 9/02 (2006.01)

D01F 9/127 (2006.01) H01J 1/304 (2006.01) H01J 3/02 (2006.01)

(86) International application number: PCT/SE2006/000487

(87) International publication number: WO 2006/115453 (02.11.2006 Gazette 2006/44)

# (54) CONTROLLED GROWTH OF A NANOSTRUCTURE ON A SUBSTRATE, AND ELECTRON EMISSION DEVICES BASED ON THE SAME

KONTROLLIERTES WACHSTUM EINER NANOSTRUKTUR AUF EINEM SUBSTRAT SOWIE DARAUF BASIERENDE ELEKTRONEN EMITTIERENDE VORRICHTUNGEN

CROISSANCE COMMANDEE D'UNE NANOSTRUCTURE SUR UN SUBSTRAT, ET DISPOSITIFS D'EMISSION D'ELECTRONS BASES SUR CELLE-CI

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

(30) Priority: **25.04.2005 SE 0500926 26.08.2005 SE 0501888 10.02.2006 US 772449 P**

- (43) Date of publication of application: **09.01.2008 Bulletin 2008/02**

- (73) Proprietor: Smoltek AB 412 92 Göteborg (SE)

- (72) Inventor: KABIR, Mohammad, Shafiqul S-412 61 Göteborg (SE)

- (74) Representative: Fritsche, Daniel et al Awapatent AB

Södra Hamngatan 37-41

Box 11394

404 28 Göteborg (SE)

- (56) References cited:

WO-A-2004/042830 WO-A-2004/109815 US-A1- 2002 185 949

- KABIR M S ET AL: "Plasma-enhanced chemical vapour deposition growth of carbon nanotubes on different metal underlayers" NANOTECHNOLOGY, IOP, BRISTOL, GB, vol. 16, no. 4, 1 April 2005 (2005-04-01), pages 458-466, XP020090998 ISSN: 0957-4484 cited in the application

- MORJAN R E ET AL: "Selective growth of individual multiwalled carbon nanotubes" CURRENT APPLIED PHYSICS, NORTH-HOLLAND, vol. 4, no. 6, November 2004 (2004-11), pages 591-594, XP004596656 ISSN: 1567-1739

- TEO K B K ET AL: "Plasma enhanced chemical vapour deposition carbon nanotubes/nanofibres how uniform do they grow?"

NANOTECHNOLOGY, INSTITUTE OF PHYSICS PUBLISHING, BRISTOL, GB, vol. 14, no. 2, 1 February 2003 (2003-02-01), pages 204-211, XP020067488 ISSN: 0957-4484 cited in the application

- KABIR M S ET AL: "Fabrication of individual vertically aligned carbon nanofibres on metal substrates from prefabricated catalyst dots" NANOTECHNOLOGY, INSTITUTE OF PHYSICS PUBLISHING, BRISTOL, GB, vol. 17, no. 3, 14 February 2006 (2006-02-14), pages 790-794, XP002394787 cited in the application

- LEE S W ET AL: "A Three-Terminal Carbon Nanorelay" NANO LETTERS, ACS, WASHINGTON DC, USA, vol. 4, no. 10, 8 April 2004 (2004-04-08), pages 2027-2030, XP002394788

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

40

50

## FIELD OF THE INVENTION

**[0001]** The present invention generally relates to nanostructures and methods for their growth. The present invention more particularly relates to methods of controlling the growth of nanostructures such as carbon nanofibers which enables manufacture of electron emission based devices such as electron beam writers and field emission displays.

1

#### **BACKGROUND**

[0002] Relentless efforts at miniaturization are bringing traditional CMOS devices to the limit where the device characteristics are governed by quantum phenomena; in such regimes, perfect control is impossible to achieve. This has engendered a need for finding alternative new materials to fabricate devices that will possess at least the same or even better performance than existing CMOS devices but with greater control.

[0003] The miniaturization of CMOS devices has hitherto been governed by a trend - often called Moore's law - in which electronic components shrink in size by half every 30 months. The International Technology Roadmap for Semiconductors (ITRS) has established a projected growth curve according to this model. The demands for speed, high integration level, high performance and low production costs attendant on such a rate of progress are very stringent Consequently, the problems associated with the physical and electrical characteristics of traditional materials used for making devices have escalated. Hence there is a need to search for alternative solutions to the problems that will ultimately impede the progress of silicon technology in the immediate future. This means that devising innovative material and process solutions is critical to sustaining the projected rate of growth.

**[0004]** The choice of new materials is however limited by factors such as compatibility with existing production methods, reproducibility of manufacture and cost. Some problems that existing technology materials have faced are as follows.

**[0005]** High power consumption due to leakage current: currently, the device performance is degraded due to high leakage current through gate oxide (which is very thin). This in turn increases the leakage current in the off state, and hence increases power consumption, which in turn reduces the life time of a battery.

**[0006]** Poor performance of Cu interconnects: due to its low resistivity, copper is used for making interconnects that are used for connecting various components to one another, as well as devices and circuits with the outside world. Due to the dramatic reduction in the size of the components, interconnects based on copper material are now showing poor performance in terms of current carrying capacity and lifetime of the wires. This in turn re-

duces the lifetime of a processor. No solution currently exists for interconnects that will efficiently connect the devices in a circuit with those outside of the circuit, in time to meet the projected demand for current density over the next several years.

[0007] Demand for high aspect ratio structures: today the aspect ratio of contact holes for interconnects in DRAM staked capacitors has reached 12:1 and is expected to increase to 23:1 by the year 2016. Creating such high aspect ratio contacts with straight walls poses substantial technological challenges, not least because void-free filling with metals (also known as vias) of such high aspect ratio features is extremely difficult.

[0008] High heat dissipation: modem microprocessors generate inordinate amounts of heat. Heat dissipation has been increasing steadily as the transistor count and clock frequency of computer processors has increased. In particular, for example, copper interconnects of the sizes required for current and future devices generate so munch heat that their electrical resistance is increased, thereby leading to a decreased capacity to carry current. However a practical solution for cooling of such systems which will not eventually exceed the power budget for processors has yet to be found.

**[0009]** In short, for all these reasons, it has become necessary to search for alternative materials and processing technology.

[0010] Carbon nanostructures, including carbon nanotubes (CNTs) andnanofibers, are considered to be some of the most promising candidates for future developments in nanoelectronics, nano-electromechanical systems (NEMS), sensors, contact electrodes, nanophotonics, and nano-biotechnology. This is due principally to their one dimensional nature, and their unique electrical, optical and mechanical properties. In contrast to the fullerenes, such as C<sub>60</sub> and C<sub>70</sub>, whose principal chemistry is based on attaching specific functionalities thereby giving rise to specific properties, CNTs offer an almost limitless amount of variation through design and manufacture of tubes of different diameters, pitches, and lengths. Furthermore, whereas the fullerenes offer the possibility of making a variety of discrete molecules with numerous specific properties, carbon nanotubes provide the possibility to make molecular-scale components that have excellent electrical and thermal conductivity, and strength. (See, e.g., Nanoelectronics and Information Technology, R. Waser (Ed.), Wiley-VCH, 2003, at chapter 19.)

[0011] Carbon nanotubes and carbon nanofibers have been considered for both active devices and as interconnect technology at least because their electrical and thermal properties and their strength. For example, the high electron mobility of carbon nanotubes (79,000 cm²/Vs) surpasses that of state-of-the-art MOSFET devices (see, e.g., Durkop, T., et al., Nano Letters, 4(1), 35, (2004)). Furthermore, the extremely high current carrying capacity of carbon nanotubes (10¹0 A/cm²) (see, e.g., Wei, B. Q., et al., Appl. Phys. Lett., 79(8), 1172, (2001)), when

compared with copper interconnects (~ 10<sup>6</sup> A/cm<sup>2</sup>), means that carbon nanotubes potentially possess the solution to the severe problems for interconnects projected in ITRS.

3

[0012] The anisotropic thermal conductivity ofnanotubes/nanofibers (6,000 W/Km) (see, e.g., Hoenlien, W., et al., IEEE Trans. Compon. and Packaging Tech., 27 (4), 629, (2004)) is also exceptionally promising for solving problems of heat dissipation.

[0013] Finally, the high E-modulus (representing the strength of a material) of individual nanotubes (as high as 1 TPa) has made them a good choice for both composite materials and for nanoelectromechanical devices. [0014] In general, it is highly desirable to fabricate electronic devices that are compatible with existing complementary metal oxide semiconductor (CMOS) fabrication techniques. A prerequisite for exploring CNTs in an industrial process is to be able to control mass production of devices with high reproducibility. Due to high purity and high yield, chemical vapor deposition (CVD) is a popular and advantageous growth method that offers the potential to grow nanotubes at an exact location with control over their length, diameter, shape and orientation.

[0015] Hence for many electronic, nanoelectromechanical systems and interconnect applications the integration possibilities of carbon nanostructures into existing CMOS-based electronic industrial manufacturing processes is expected to be a ground breaking technological breakthrough. However, there are many engineering and materials issues inherent to CMOS-compatible device fabrication processes that need to be addressed before such integration can take place. Solutions to these issues have so far been long-awaited.

[0016] For instance, there are problems related to growth of nanostructures. Although numerous techniques have been developed and demonstrated to produce carbon based nanostructures, all possess drawbacks regarding mass production and integration into existing industry manufacturing processes. Prominent drawbacks are: (a) control over predictable morphology with either semiconducting or metallic properties, (b) precise localization of the grown individual structures, and (c) predictable electrical properties at the interface between the grown nanostructures and the substrate. There is no known single solution to solve all the aforementioned drawbacks. The most prominent techniques for synthesizing carbon nanostructures include arc discharge (see, e.g., lijima, S., Nature, 354, 56, (1991); and Kratschmer, W.; Lamb, L. D.; Fostiropoulos, K.; Huffman, D. R., Nature, 347, 354, (1990)), laser vaporization (see, e.g., Kroto, H. W.; Heath, J. R.; O'Brien, S. C.; Curl, R. F.; Smalley, R. E. Nature, 318, 162, (1985)), catalytic chemical-vapor deposition (CCVD), also referred to as CVD, (Cassell, A. M.; Raymakers, J. A.; Jing, K.; Hongjie, D., J. Phys. Chem. B, 103, (31), (1999)), and catalytic plasma enhanced chemical-vapor deposition (C-PECVD) (Cassell, A. M.; Qi, Y.; Cruden, B. A.; Jun, L.; Sarrazin, P. C.; Hou Tee, N.; Jie, H.; Meyyappan, M.,

Nanotechnology, 15(1), 9, (2004); and Meyyappan, M.; Delzeit, L.; Cassell, A.; Hash, D., Plasma Sources, Science and Technology, 12(2), 205, (2003)). Due to high purity and high yield, chemical vapor deposition (CVD) is a popular and advantageous growth method, and indeed, among all of the known growth techniques, CMOS compatibility has been demonstrated only for the CCVD method. (See, Tseng, et al. (Tseng, Y.-C.; Xuan, P.; Javey, A.; Malloy, R.; Wang, Q.; Bokor, J.; Dai, H. Nano Lett. 4(1), 123-127, (2004)) where a monolithic integration of nanotube devices was performed on n-channel semiconductor (NMOS) circuitry.)

[0017] There are specific problems related to control of the properties of grown materials. Even though numerous different alternative growth methods exist for growing carbon nanostructures, controlling the interface properties between the nanostructures and the substrates, the body of the nanostructures, and the tip of the nanostructures are not yet demonstrated to be well controlled by utilizing a single method of growth.

[0018] CVD typically employs a metal catalyst to facilitate carbon nanostructure growth. The main roles of the catalyst are to break bonds in the carbon carrying species and to absorb carbon at its surface and to reform graphitic planes through diffusion of carbon through or around an interface (see, e.g., Kim, M. S.; Rodriguez, N. M.; Baker, R. T. K., Journal of Catalysis, 131, (1), 60, (1991); and Melechko, A. V.; Merkulov, V. I.; McKnight, T. E.; Guillorn, M. A.; Klein, K. L.; Lowndes, D. H.; Simpson, M. L., J. App. Phys., 97(4), 41301, (2005)).

[0019] However, the growth of nanotubes is usually carried out on silicon or other semiconducting substrates. Growth from such metal catalysts on conducting metal substrates or metal underlayers is almost lacking. This is because it has been found that it is hard to make a good contact between a growing nanostructure and a conducting substrate with good quality grown nanostructures in terms of control over diameter, length and morphology. Nevertheless, for making CMOS-compatible structures, it is necessary to use a conducting substrate. In particular, this is because a metal substrate, or base layer, acts as bottom electrode for electrical connection to the nanostructures.

[0020] Nevertheless, growth of nanostructures on CMOS compatible conducting substrates has proved to be far from trivial, at least because different metals require different conditions, and also because it has proven difficult to control the properties of the nanostructures grown on such substrates with predictable control over diameter, length and morphology of the grown structures and with predictable interface properties between the nanostructures and the substrate.

[0021] A method for producing arrays of carbon nanotubes on a metal underlayer, with a silicon buffer layer between the metal underlayer and a catalyst layer, is described in U.S. Patent Application Publication No. 2004/0101468 by Liu et al. According to Liu, the buffer layer prevents catalyst from diffusing into the substrate

40

25

40

45

50

55

and also prevents the metal underlayer from reacting with carbon source gas to, undesirably, form amorphous carbon instead of carbon nanostructures. In Liu, the process involves, inconveniently, annealing the substrate in air for 10 hours at 300-400 °C to form catalyst particles, via oxidation of the catalyst layer, prior to forming the nanostructures. Each catalyst particle acts as a seed to promote growth of a nanostructure. The method of Liu, however, does not permit control of the composition or properties of the nanostructures and the nanotubes produced are curved and disorganized.

[0022] An additional goal is fabrication of carbon based nano-electro mechanical structures (NEMS). Extensive theoretical analysis on two-terminal and three-terminal carbon based NEMS (C-NEMS) structures were performed by Dequesnes et al. (Dequesnes, M.; Rotkin, S.V.; Aluru, N. R., Nanotechnology, 13(1),120, (2002)) and Kinaret et al. (Kinaret, J. M.; Nord, T.; Viefers, S., Applied Physics Letters, 82(8), 1287, (2003)) respectively. The model developed by Kinaret et al. for three-terminal NEMS device consists of a conducting carbon nanotube (CNT) placed on a terraced Si substrate and connected to a fixed source electrode which they have called it "nanorelay." Recently Lee et al. (Lee, S. W. L., et al., Nano Letters, 4(10), 2027, (2004)) have demonstrated the characteristics of such three terminal nanorelay structures experimentally. However, the experimental approach by Lee et al. for fabricating such devices is time consuming and the technology is heavily dependent on the sonicated CNF solutions which usually do not possess any control over the length and the diameter of the CNF: the functional part of the device. Therefore, it is desirable to develop a technology for fabricating such structures with predictable behavior.

**[0023]** Accordingly, there is a need for a method of growing carbon nanostructures on a metal substrate in such a way that various properties of the nanostructures can be controlled.

**[0024]** The discussion of the background to the invention herein is included to explain the context of the invention. This is not to be taken as an admission that any of the material referred to was published, known, or part of the common general knowledge as at the priority date of any of the claims.

**[0025]** Throughout the description and claims of the specification the word "comprise" and variations thereof, such as "comprising" and "comprises", is not intended to exclude other additives, components, integers or steps.

#### **SUMMARY OF THE INVENTION**

[0026] A nanostructure assembly as defined by claim 1.

**[0027]** A multilayer interface between a catalyst and a substrate having: at least one layer to control morphology, and at least one layer to control an electrical interface between a nanostructure and base layer. In the multilayer interface, at least one layer is preferably of a semicon-

ducting material such as silicon or germanium.

**[0028]** A nanostructure supported upon a metal substrate, wherein metal is interdiffused with a semiconducting layer between the nanostructure and the substrate.

**[0029]** The present invention also contemplates forming nanostructures at high temperatures but without prior annealing of a catalyst layer on which the nanostructures are grown. Preferably the temperatures employed are less than 750 °C.

**[0030]** The present invention also contemplates the formation of nanostructures formed not of carbon but of other solid state materials such as GaN, GaAs, InP, InGaN, ZnO, Si. In general, semiconducting nanostructures are based on a combination such as II-VI or III-V materials from the periodic table of the elements. Examples of appropriate conditions for making such nanostructures are further described herein.

**[0031]** The present invention also contemplates a "lift-off" method of fabricating individual fibers: lift-off of polymer layer to provide individual layers.

**[0032]** Nanostructures formed according to the present invention may be used as interconnects, current carrying conductors, anisotropic heat directing media, can be integrated into components: active/passive devices like diodes, transistors, capacitors, inductors, field emitting devices, optical devices, X-ray emitting devices, sensors, electrochemical probes etc.

**[0033]** By having a layer of material between the catalyst and the substrate, it is possible to influence the texture of the final catalytic particles and hence influence the growth mechanism and morphology of the grown nanostructures.

**[0034]** A precursor for a nanostructure assembly, comprising: a conducting substrate;

**[0035]** a catalyst layer; and a plurality of intermediate layers between the conducting substrate and the catalyst layer, the plurality of intermediate layers including at least one layer to affect morphology of a nanostructure to be formed on the catalyst layer and at least one layer to affect electrical properties of an interface between the support layer and the nanostructure.

**[0036]** A carbon nanostructure assembly comprising: a conducting substrate; a layer of amorphous silicon on the conducting substrate; and a layer of catalyst on the layer of amorphous silicon, wherein the carbon nanostructure is disposed on the catalyst.

**[0037]** A carbon nanostructure, comprising: a substantially straight generally cylindrical carbon nanostructure having a conical angle less than 2 degrees.

[0038] An array of carbon nanostructures supported on a substrate, wherein each carbon nanostructure in the array comprises: a conducting substrate; a plurality of intermediate layers on the conducting substrate; a catalyst layer on the intermediate layers; and a carbon nanostructure on the catalyst layer, wherein said each carbon nanostructure is spaced apart from any other carbon nanostructure in the array by between 70 nm and 200 nm.

[0039] A method of forming a nanostructure, compris-

ing: depositing a layer of semiconducting material on a conducting substrate; depositing a catalyst layer on the semiconducting layer; without first annealing the substrate, causing the substrate to be heated to a temperature at which the nanostructure can form; and growing a nanostructure on the catalyst layer at the temperature.

**[0040]** A method of forming a nanostructure precursor, comprising: depositing a sacrificial layer on a conducting substrate; forming a plurality of apertures in the sacrificial layer; depositing an intermediate layer of semiconducting material over the sacrificial layer and on the substrate in the apertures; depositing a catalyst layer over the intermediate layer; and lifting off the sacrificial layer to leave portions of the intermediate layer and catalyst layer corresponding to the apertures on the substrate.

[0041] A field emission device according to claim claim 22.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

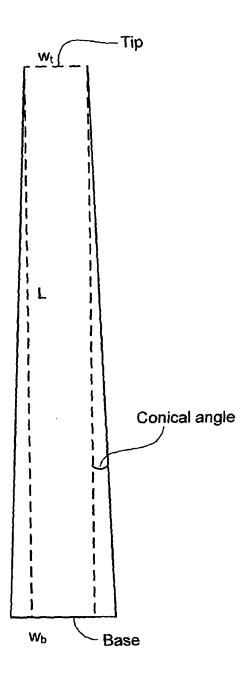

[0042] FIG. 1 shows a schematic of a carbon nanofiber.

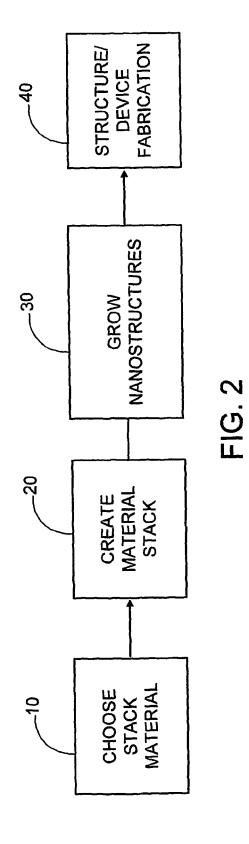

[0043] FIG. 2 shows a flow-chart of an overall process according to the present invention.

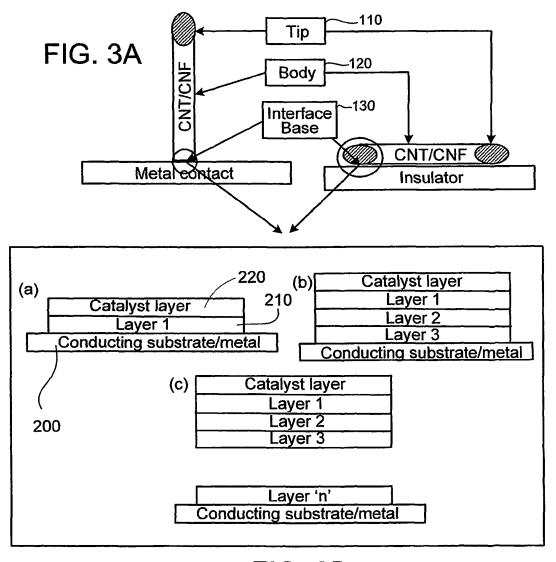

**[0044]** FIGS. 3A and 3B show various configurations of the present invention.

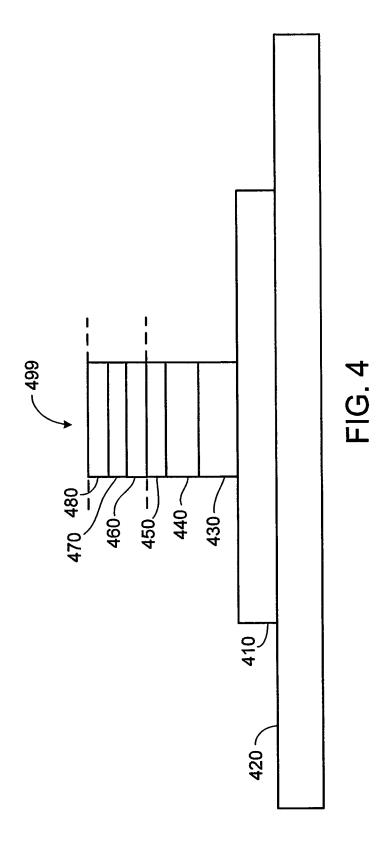

**[0045]** FIG. 4 shows a multilayer stack between a metal layer and a nanostructure, and having various segments of different functionalities.

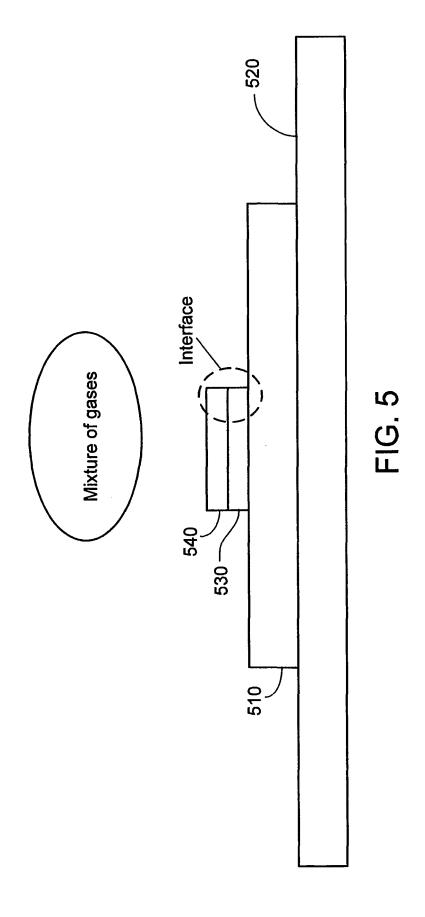

**[0046]** FIG. 5 shows a step in creation of an individual nanostructure.

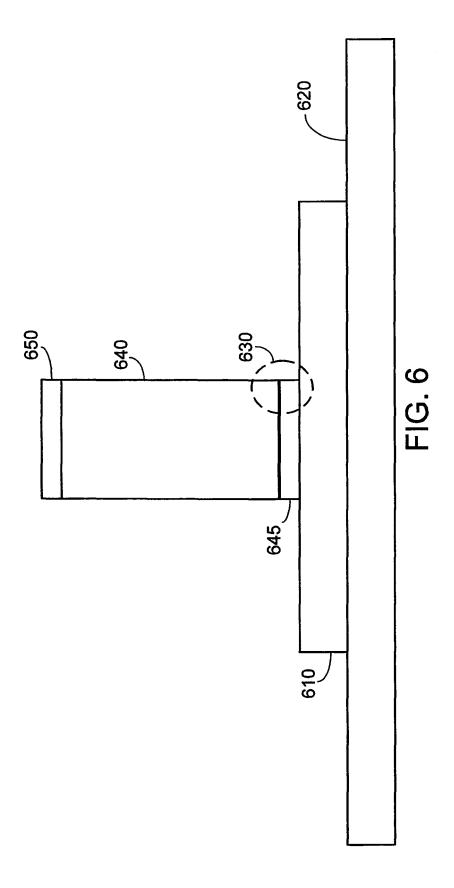

**[0047]** FIG. 6 shows an individual nanostructure with a single layer between the nanostructure body and a metal substrate.

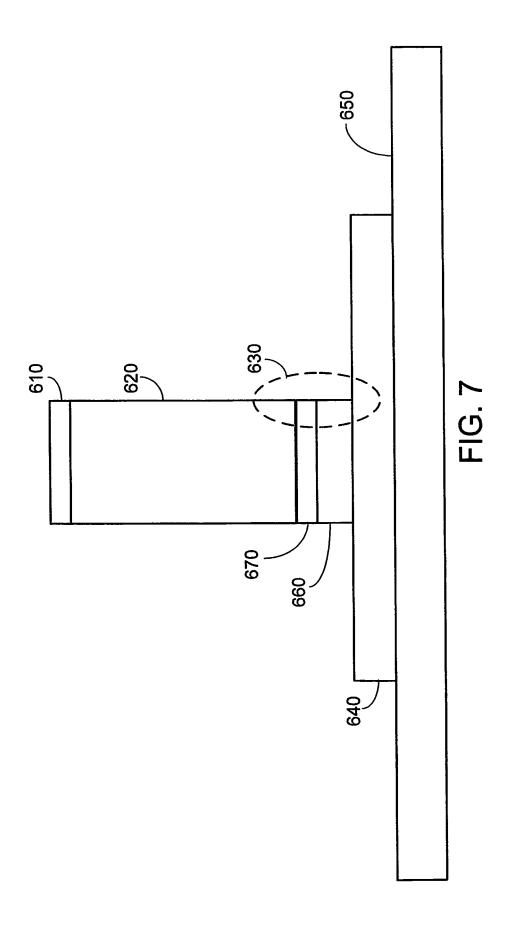

[0048] FIG. 7 shows an individual nanostructure.

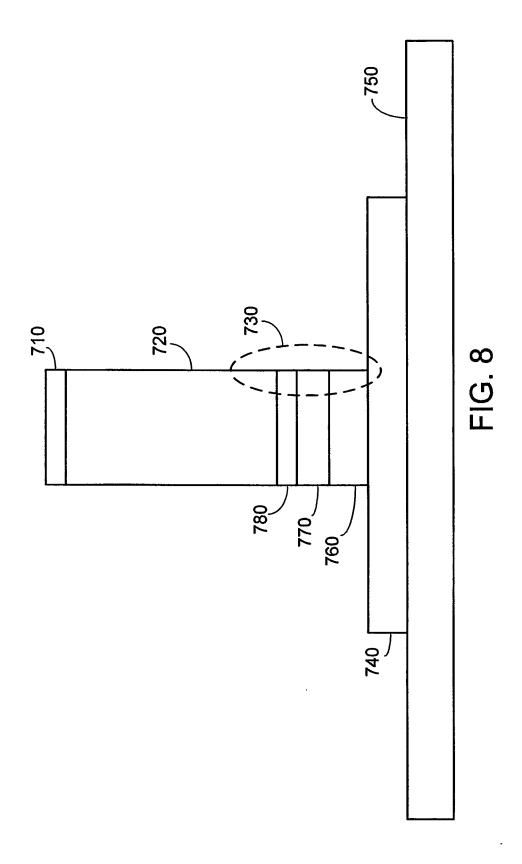

**[0049]** FIG. 8 shows an individual nanostructure having a multilayer stack.

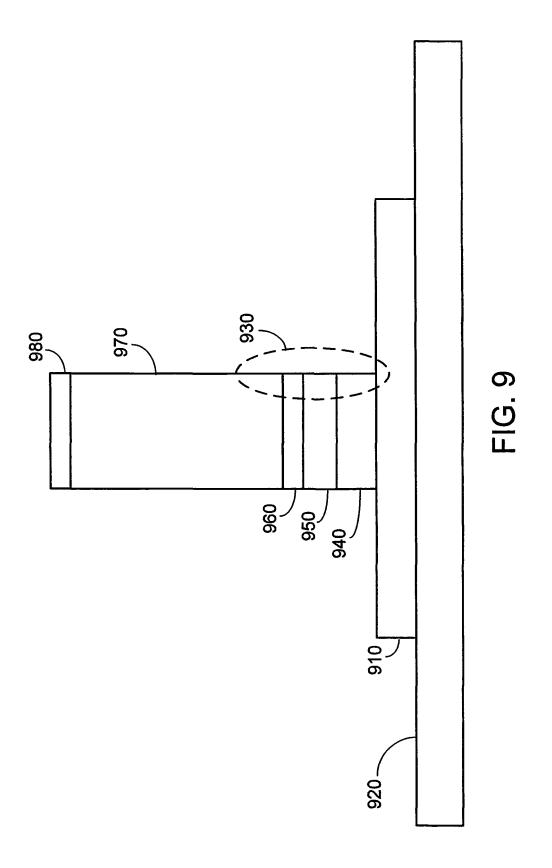

[0050] FIG. 9 shows an embodiment of a nanostructure.

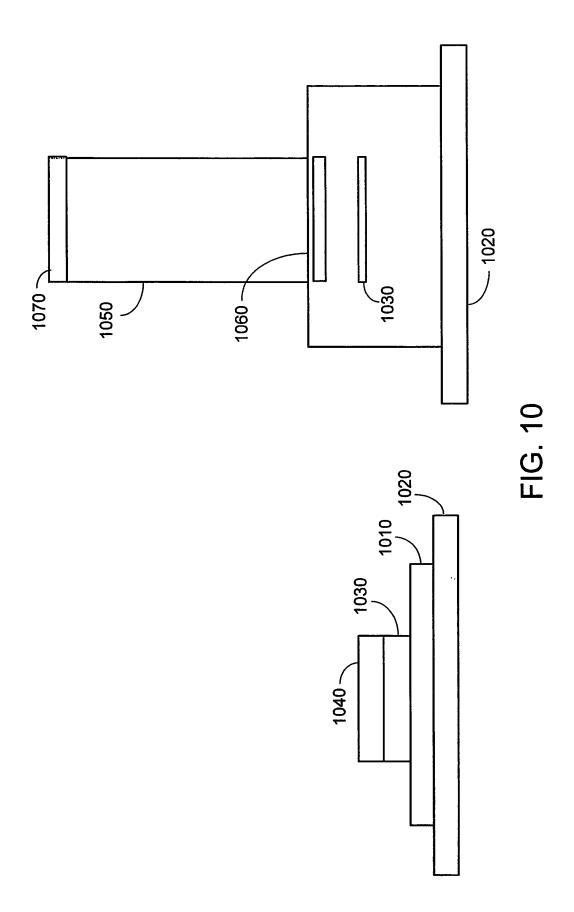

**[0051]** FIG. 10 shows an intermediate stage in a process of making a nanostructure.

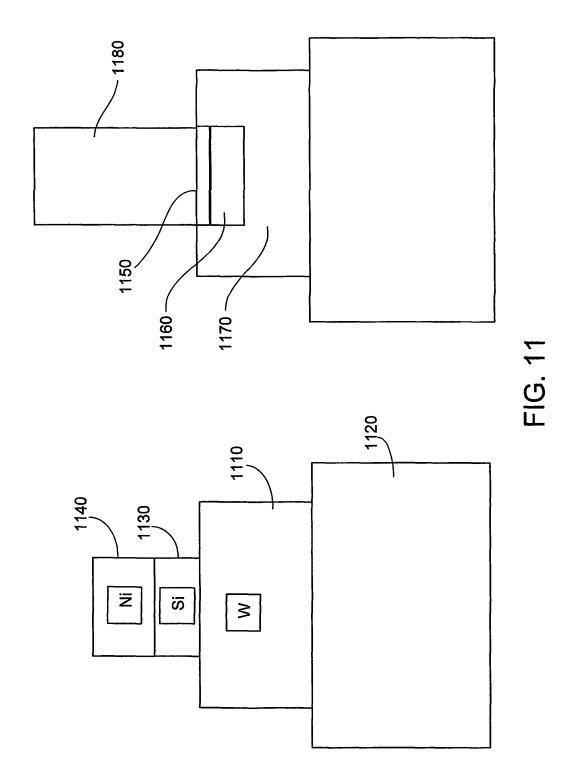

[0052] FIG. 11 shows an example of growth of a nanostructure.

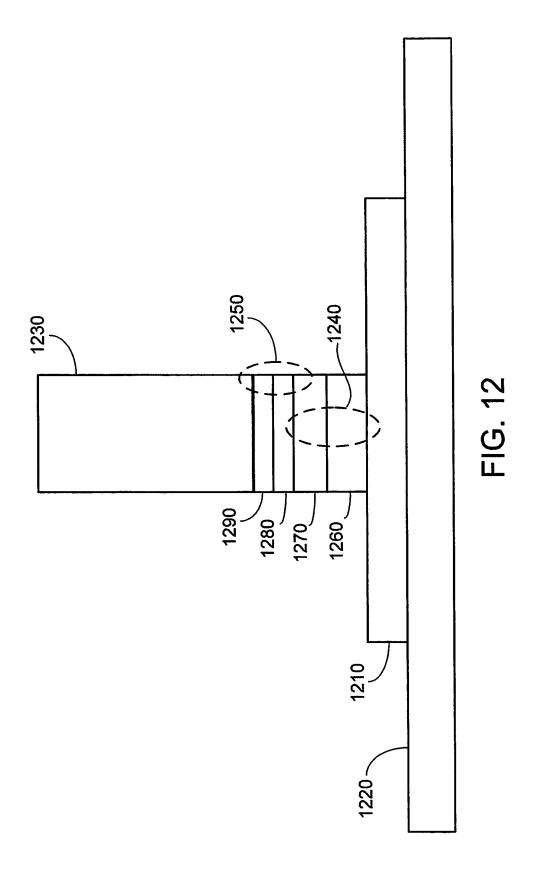

**[0053]** FIG. 12 shows layers that control properties of an individual nanostructure.

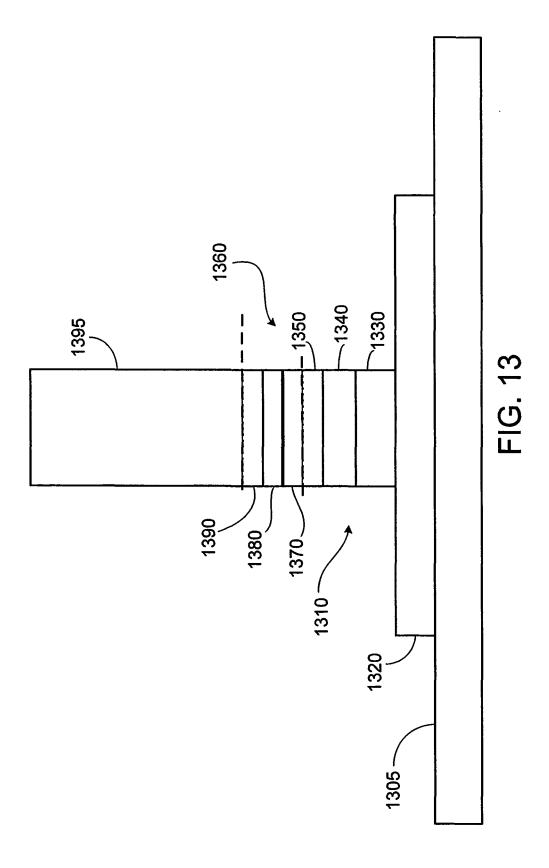

**[0054]** FIG. 13 shows an individual nanostructure as part of an electric circuit

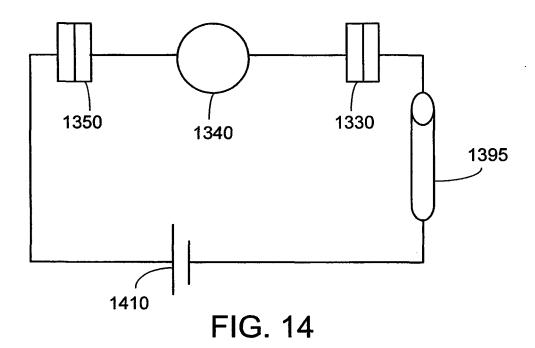

**[0055]** FIG. 14 shows an electric circuit configured to use a carbon nanostructure.

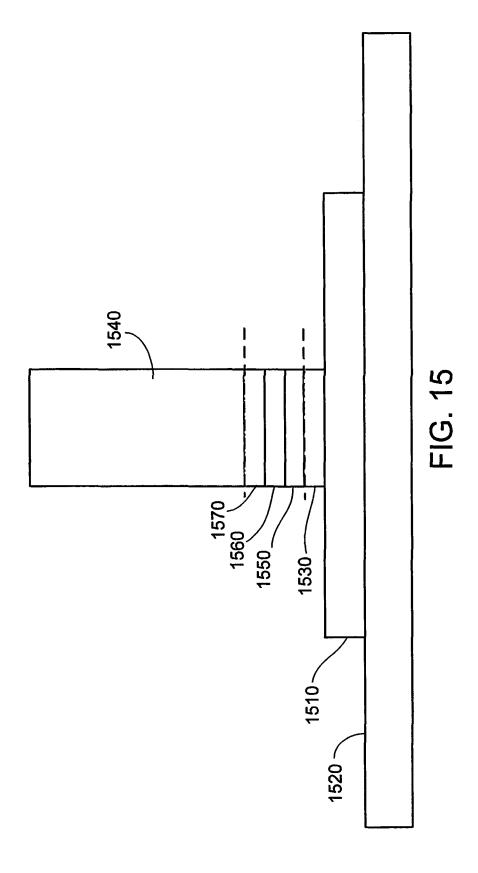

[0056] FIG. 15 shows an individual nanostructure as part of an electric device.

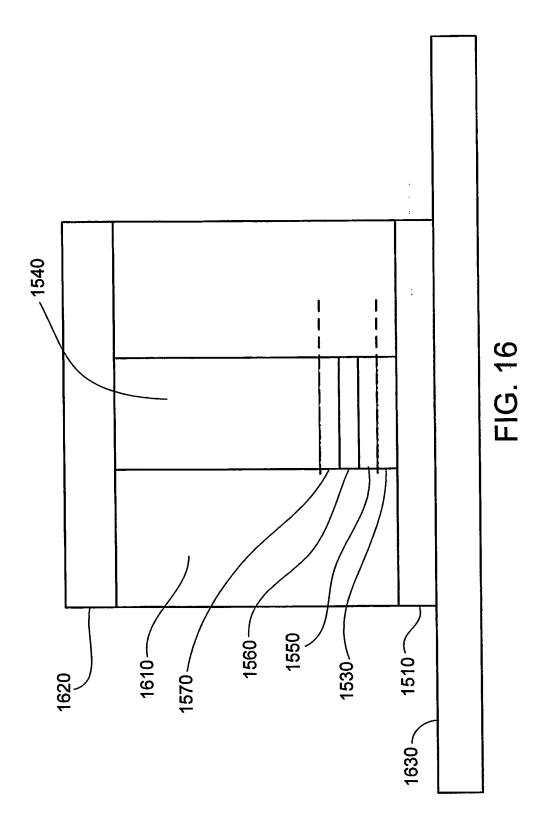

[0057] FIG. 16 shows an individual nanostructure as an electric/optical device.

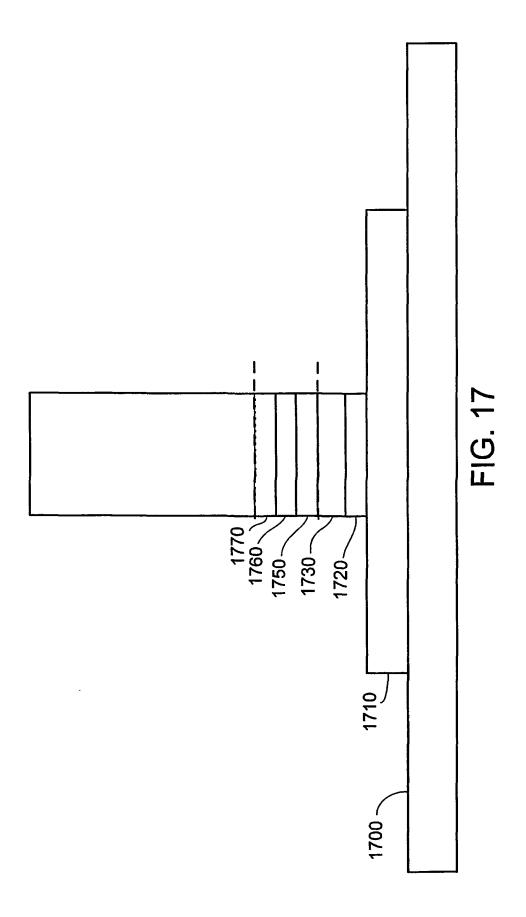

[0058] FIG. 17 shows an individual nanostructure as part of a Schottky Barrier.

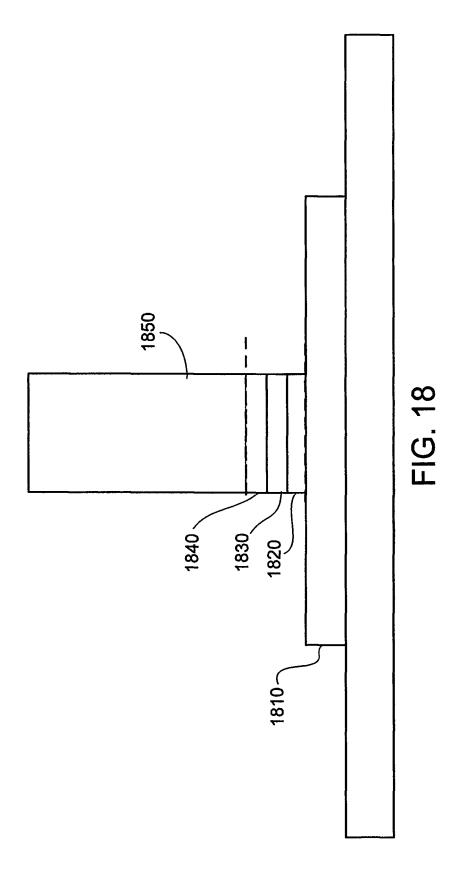

**[0059]** FIG. 18 shows an individual nanostructure as part of a Schottky Barrier.

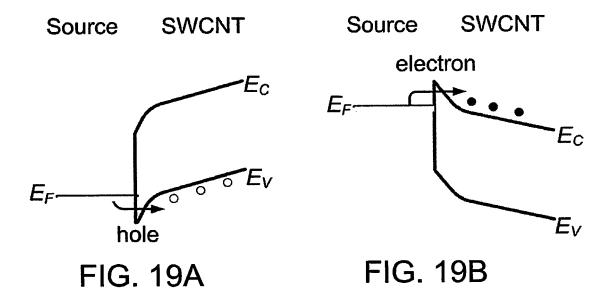

**[0060]** FIG. 19 shows an energy level diagram for an interface in a structure according to FIG. 18.

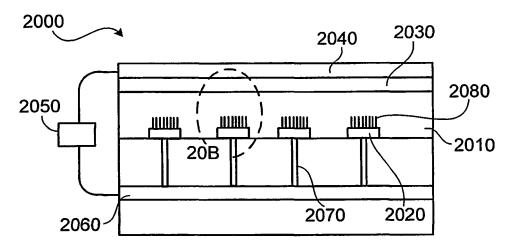

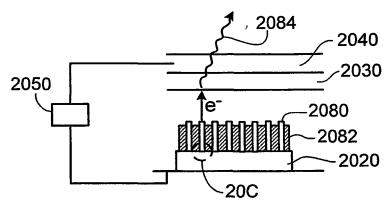

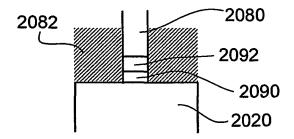

**[0061]** FIGs. 20A - 20C show various views of a field emission device using nanostructures according to the present invention.

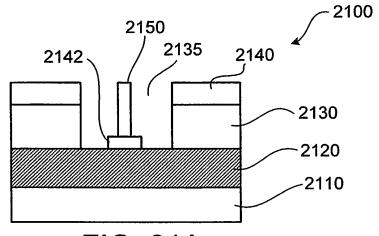

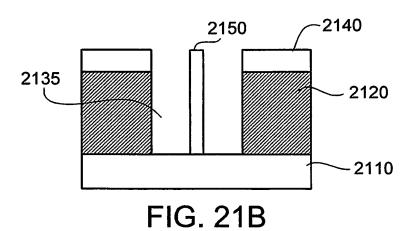

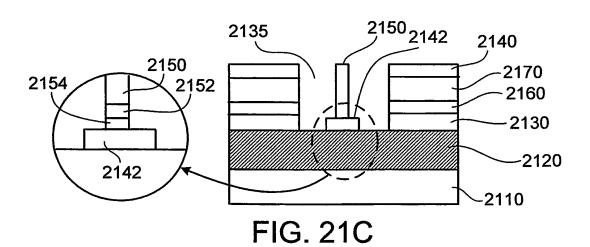

**[0062]** FIGs. 21A - 21C show various embodiments of an electron-beam emitter using nanostructures according to the present invention.

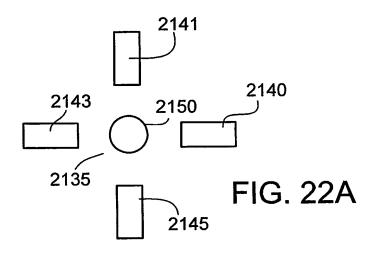

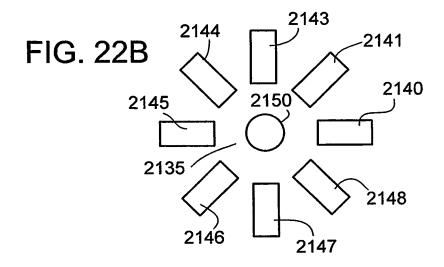

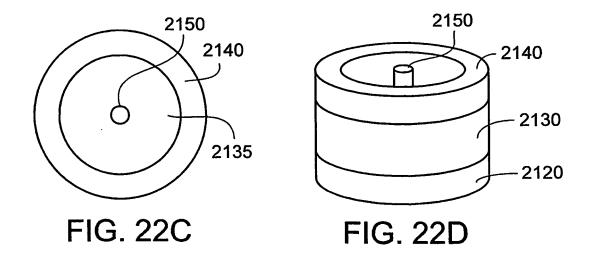

**[0063]** FIGs. 22A - 22D show various embodiments of electrode configurations in an electron-beam writer using nanostructures according to the present invention.

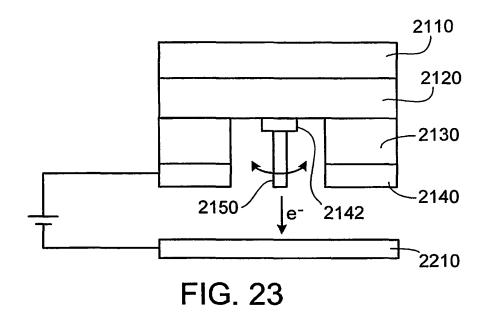

[0064] FIG. 23 shows an electron-beam writer configured to write on a substrate.

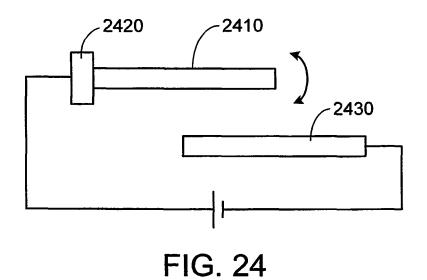

**[0065]** FIG. 24 shows a horizontal configuration of an electron-beam writer.

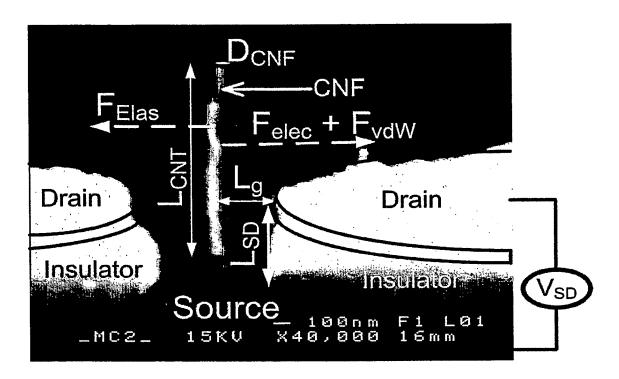

**[0066]** FIG. 25 shows an exemplary electron-beam writer using a nanostructure.

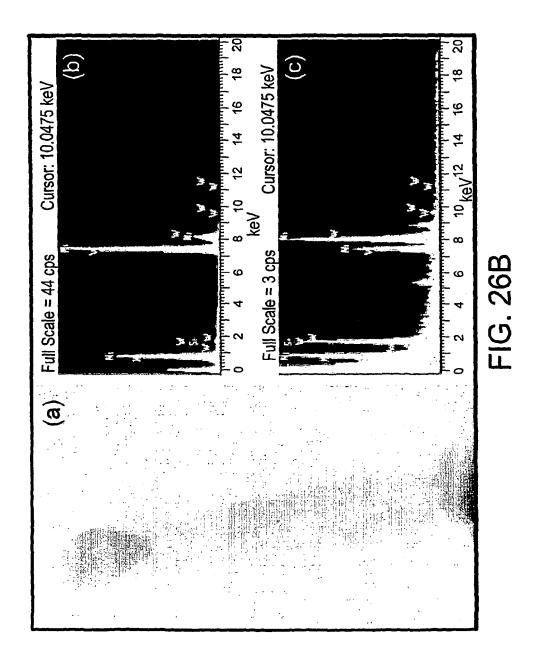

[0067] FIG. 26A is a transmission electron microscopy (TEM) micrograph of a carbon nanofiber grown on a tungsten underlayer. FIG. 26B shows: (a) TEM micrograph of a nanofiber grown on a W metal underlayer; (b) a corresponding EDS spectrum taken at the tip of the fibers (catalyst region); and (c) an EDS spectrum taken at the base of the fibers (underlayer region).

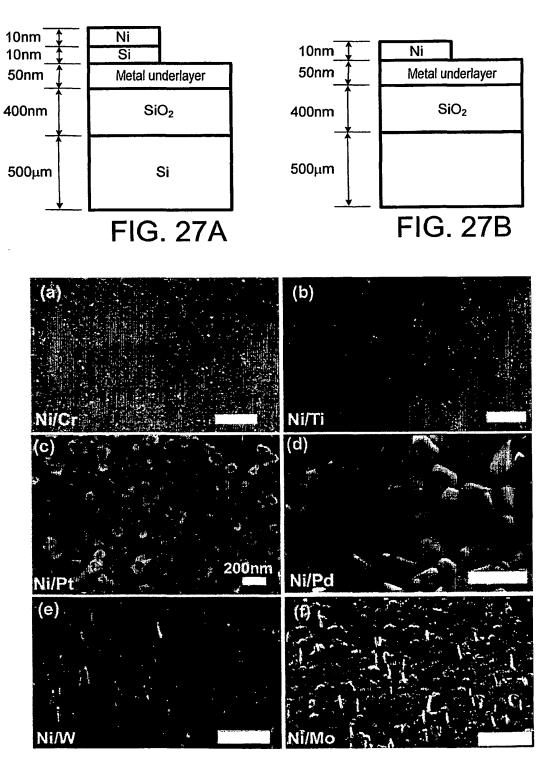

**[0068]** FIGs. 27A & B show schematics of a layers on a conducting underlayer on a support, with Si as intermediate layer (FIG 27A), and Ni catalyst deposited directly on the metal underlayer (FIG. 27B).

[0069] FIG. 28: SEM micrographs of metal underlayers after growth sequence. Only W and Mo metal underlayers facilitated appreciable CNT growth. In this set of experiments Ni was evaporated directly on the metal underlayers. Standard growth conditions ( $V_B = -400 \text{ V}$ ,  $C_2H_2$ :NH $_3$  =1:5, time =15 min., T=700 °C) were used for all cases. All scale bars are 1  $\mu$ m except FIG. 27(c).

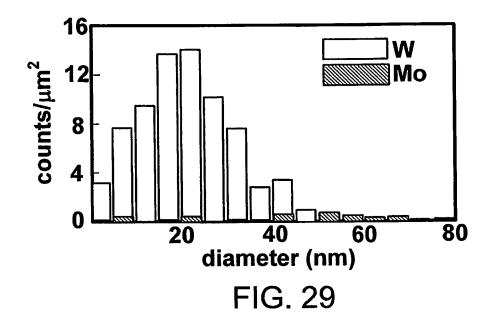

[0070] FIG. 29. Density of individual nanostructures  $\mu\text{m}^{-2}$  area for the case of Mo and W metal underlayers without amorphous Si layer.

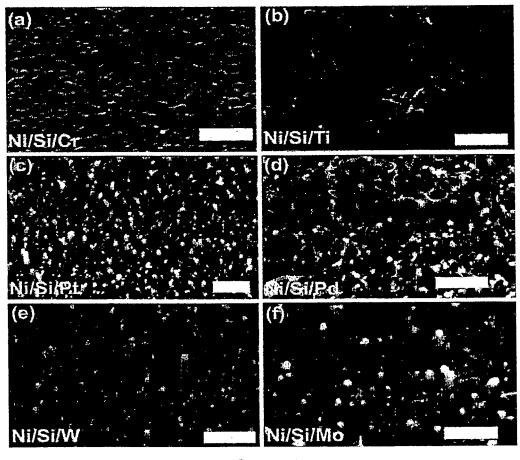

[0071] FIG. 30. SEM micrograph of the samples after 15 min. of CVD growth. The presence of Si facilitated the growth of nanotubes on some metal underlayers which was not possible in the previous set of experiments. Standard growth conditions ( $V_B = -400 \text{ V}, C_2H_2: \text{NH}_3 = 1:5$ , time =15 min, T=700 °C) were used for all cases. All scale bars are 1  $\mu m$ .

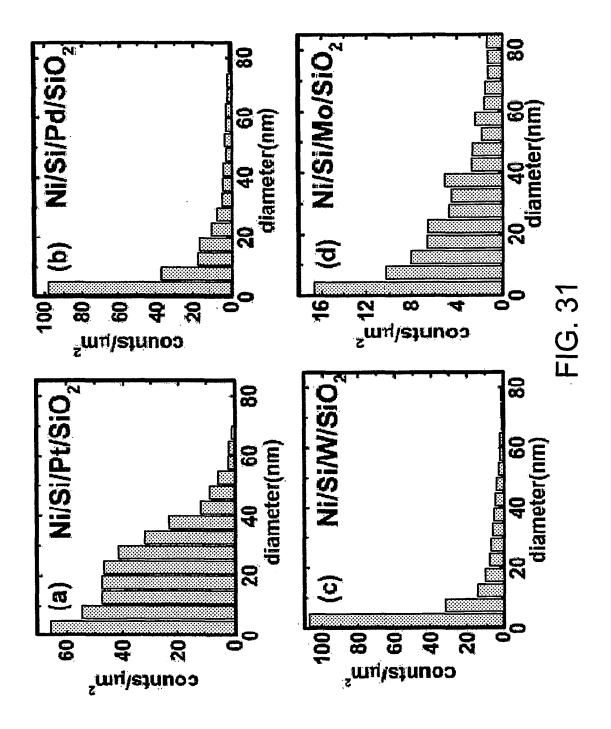

**[0072]** FIG. 31. Particle size distribution for four most promising metal underlayer samples: (a) platinum; (b) palladium; (c) tungsten; (d) molybdenum. The nanotube diameter distribution was plotted averaging three different images as shown in FIG. 29 for each metal underlayer.

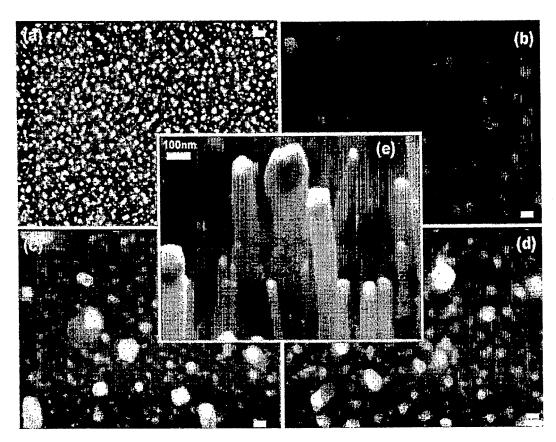

[0073] FIG. 32. Top-view SEM images of CNTs grown on (a) platinum; (b) palladium; (c) tungsten; (d) molybdenum. The middle inset (e) is a side view image showing the growth of very thin tubes (<10 nm) among thick tubes. All scale bars are 100 nm.

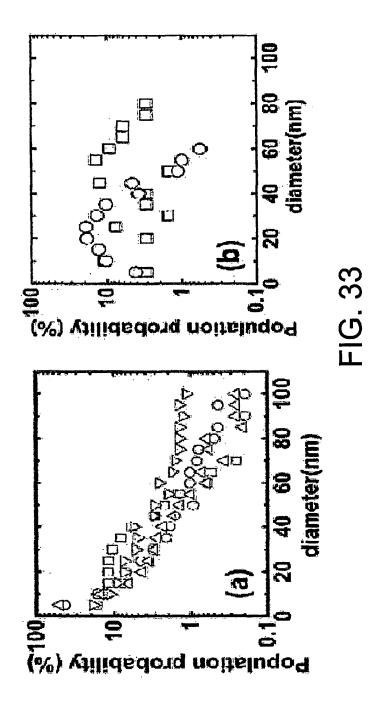

**[0074]** FIG. 33. Size distribution of CNTs: (a) metal underlayer with amorphous Si layer; square-platinum-390 counts  $\mu$ m<sup>-2</sup>; circle-palladium-226 counts  $\mu$ m<sup>-2</sup>; up-triangle-tungsten-212 counts  $\mu$ m<sup>-2</sup>; downtriangle-molybde-

num-89 counts  $\mu$ m<sup>-2</sup> and (b) metal underlayer without amorphous Si layer; square-molybdenum-5 counts  $\mu$ m<sup>-2</sup>; circle-tungsten-73 counts  $\mu$ m<sup>-2</sup>.

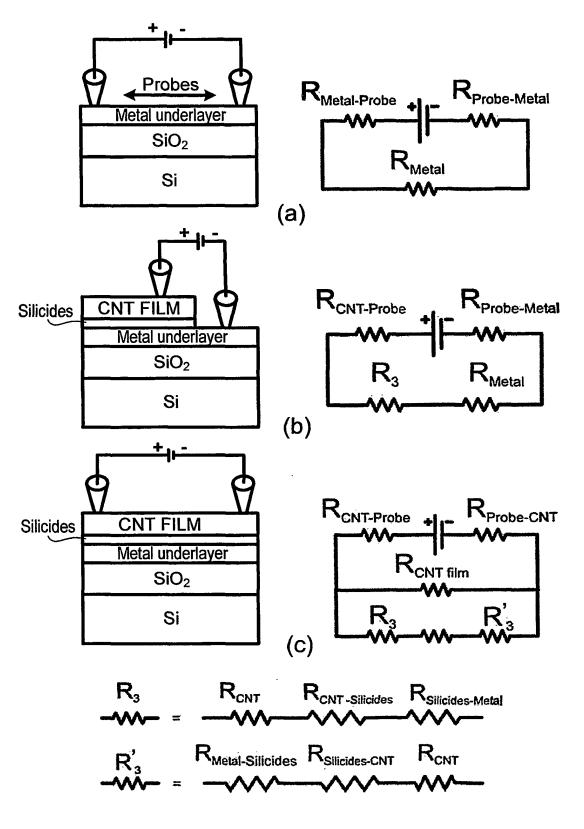

**[0075]** FIG. 34: Equivalent circuit diagram of the electrical measurements: (a) metal-metal configuration; (b) metal-CNT configuration; (c) CNT-CNT configuration.

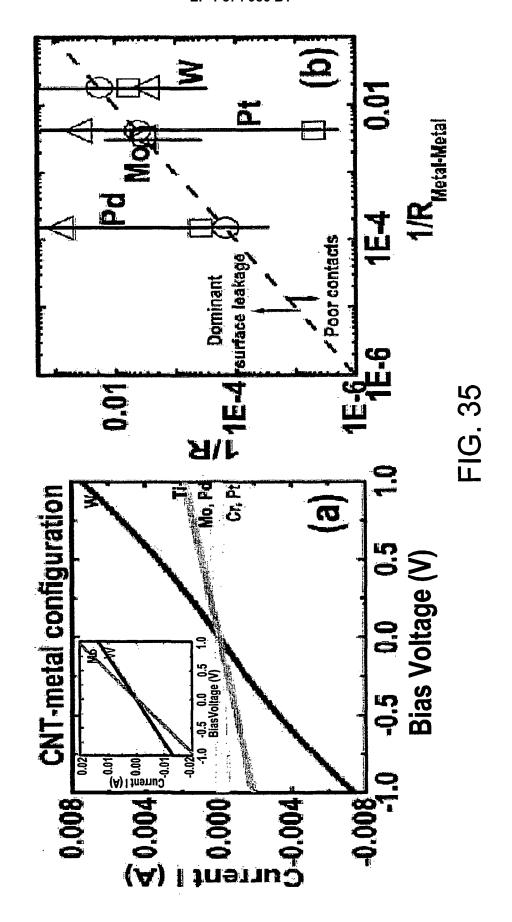

[0076] FIG. 35: (a) I-V characteristics of metal underlayers for CNT-metal configuration on samples with an amorphous Si layer; inset: the same measurements for samples without the Si layer. (b) Conductance deviations for samples with the amorphous Si layer, plotted in loglog scale. The straight dotted line represents the metalmetal conductance for different metal underlayers. Current is dominated by surface leakage if the conductance value is above the dotted line and poor contacts are considered if it is below the dotted line. Circle-metal-metal configuration; square-CNT-CNT configuration; triangle-CNT-metal configuration.

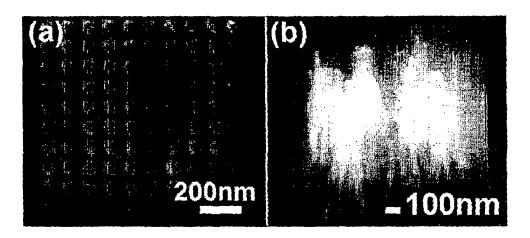

[0077] FIG. 36: SEM micrograph of grown fibers on a W metal underlayer. (a) Represents the fibers grown from 100 nm dots with 500 nm pitch. All catalyst dots nucleated for growth of more than one fiber. Inset shows no break up of the catalyst after heating. (b) After growth when Ni catalyst was deposited on W directly. No growth is observed. (c) Fibers grown from prefabricated 50 nm dots with 1  $\mu$ m pitch. Most of the dots nucleated to grow individual fibers. (d) Individual fibers grown from 50 nm prefabricated catalyst dots with 500 nm pitch.

[0078] FIG. 37: SEM micrograph of grown fibers on Mo metal underlayer. (a) Represents the fibers grown from a film of Ni/a-Si catalyst layer. (b) Grown fibers from a 2  $\mu m$  catalyst stripe. Inset picture is taken from the middle of the stripe. (c) Fibers grown from prefabricated 100 nm dots. Most of the dots nucleated to grow more than one fiber. (d) Individual fibers were grown from 50 nm prefabricated catalyst dots.

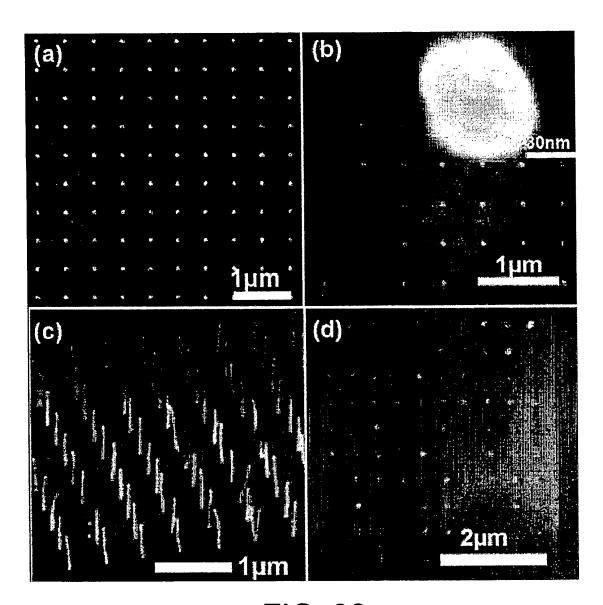

[0079] FIG. 38: Sequential presentation of the results at different stages of the fabrication procedures: (a) after lithography and metal deposition where 1200  $\mu$ C cm-2 dose was applied, (b) after an annealing step before growth of CNF. A high resolution image of a dot is shown in the inset (c) after growth of CNFs at 700 °C for 20 min (from 60° tilted substrates) and (d) after a growth step of CNFs where no intermediate amorphous Si layer was applied, resulting in no growth of CNFs.

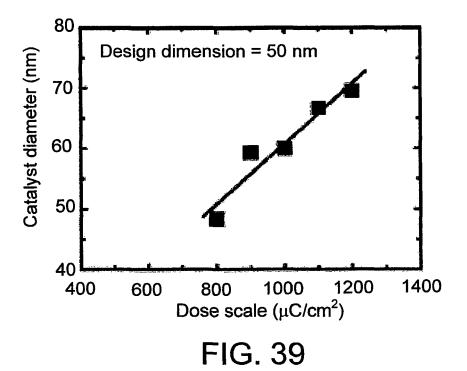

**[0080]** FIG. 39: Diameter as a function of dose for dots after the lithography step. A linear fit of the measured values is indicated by a straight line.

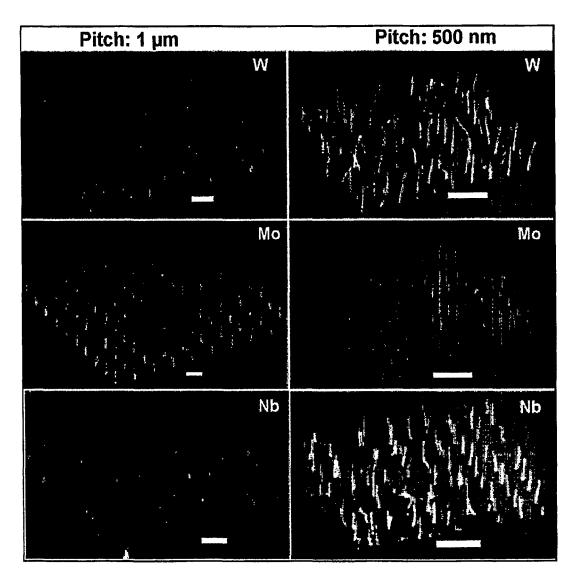

[0081] FIG. 40: SEM micrograph of the grown CNFs for dose scale 800  $\mu$ C cm<sup>-2</sup> for three different metal underlayers. The column corresponds to 1  $\mu$ m and 500 nm pitch respectively. Micrographs are taken from 60° tilted substrates. All scale bars are 1  $\mu$ m.

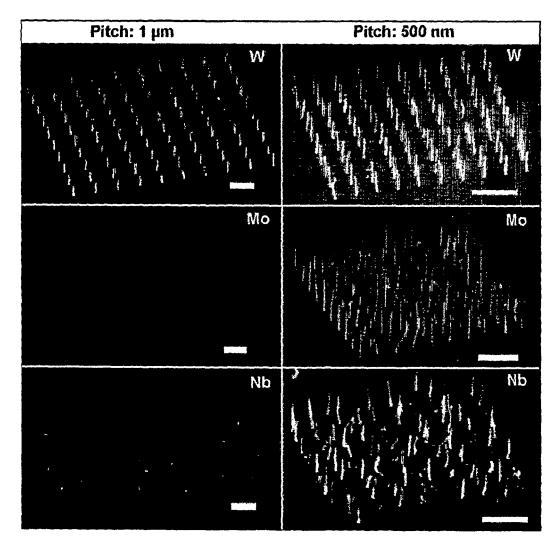

[0082] FIG. 41: SEM micrograph of the grown CNFs for dose scale 1200  $\mu$ C cm<sup>-2</sup> for three different metal underlayers. The column corresponds to 1  $\mu$ m and 500 nm pitch respectively. Micrographs are taken from 60° tilted substrates. All scale bars are 1  $\mu$ m.

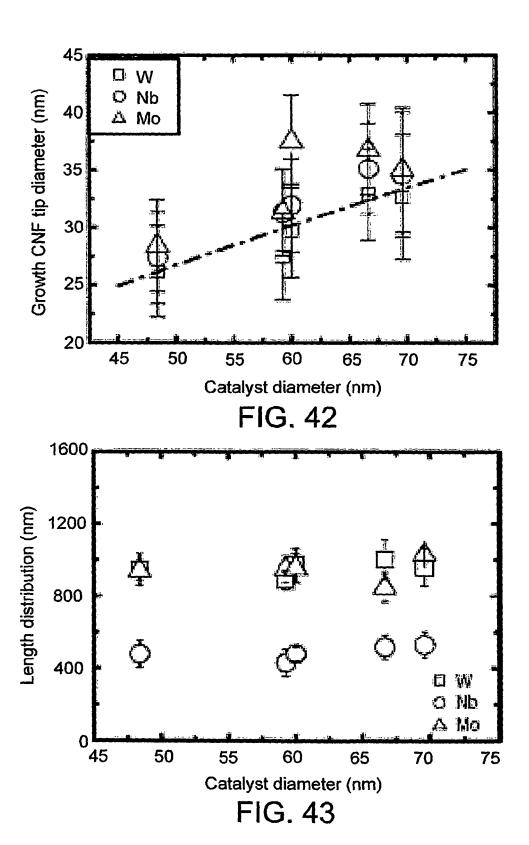

**[0083]** FIG. 42: Tip diameter of grown CNFs as a function of the catalyst diameter. Error bars indicate the standard deviation from the average value. The trend of the average value is indicated by a dashed-dotted line for the W substrate.

**[0084]** FIG. 43: Average length distribution is plotted as a function of the catalyst diameter for different metal underlayers. Error bars represent the corresponding standard deviation.

10 [0085] FIG. 44: Pitch induced limitations on high density growth of CNFs: (a) no predominant catalyst cluster conglomeration is present after the annealing step (top view), and (b) forest-like growth of CNFs after growth resembles the growth from the film of the catalyst (from 60° tilted substrate).

#### **DETAILED DESCRIPTION**

Overview

20

25

30

40

45

[0086] The present invention is directed to processes for making nanostructures, singly, or in arrays, on a conducting substrate. In particular, the processes of the present invention permit choices of material, and sequences of materials, lying between the substrate and the base of the nanostructure, to control various properties of the interface between the nanostructure and the substrate, properties of the body of the nanostructure, and the composition of the tip of the nanostructure. It is preferable that the nanostructures form columns that grow perpendicularly, or almost perpendicularly up from the substrate. However, this does not exclude the possibility to grow the nanostructures at other angles from the substrate such as on the substrate, (i.e., parallel to the substrate), or at an inclined angle other than 90°.

[0087] Accordingly, the present invention relates to: a method of growing/depositing nanostructures utilizing existing CMOS technology; a method of growing nanostructures on CMOS compatible conducting substrates and glass substrate and flexible polymer substrates used in areas that utilize thin film technology; a method to control the chemical interactions and hence controlling the end chemical compounds in the nanostructures; and a method to control the chemical reactions by having multilayer material stacks consisting of at least one intermediate layer between the substrate and a catalyst layer, wherein the intermediate layer is not of the same material as either the catalyst layer or the conducting substrate.

[0088] The present invention therefore provides a method for integrating nanostructures into CMOS technology and to achieve downscaling, higher component density and new functionality in, e.g., integrated circuits. [0089] The ability to grow nanostructures on different metal underlayers (metal substrates) is important for several other reasons, including the fact that the identity of the metal is an additional parameter that can be tuned to control the parameters of grown nanostructures such as height, diameter, density, etc., and because different

20

25

35

40

45

50

metal work functions can be exploited to control the height of the Schottky barrier between the metal underlayers and the nanostructures, thus permitting control over device functionality.

**[0090]** By controlling the choice of material stacks and the sequence of different materials, the layers in a stack can be used to control properties of the grown/deposited nanostructures.

**[0091]** In particular, by varying the materials and sequence of the materials the properties of the following can be controlled: the interface between the nanostructure and the substrate can be controlled to have properties that include, but are not limited to, Ohmic barriers, Schottky contacts, or controllable tunneling barrier(s); the body of the nanostructures; and the chemical composition of the tip of the nanostructures.

[0092] By controlling the properties of these three parts (the interface, the body, and the tip), different structures, components and devices can be fabricated which can be used in different applications. By controlling the properties of these three parts in combination with different structures, components and devices, different functionality can be achieved. For example, the tip of the nanostructure can be tailored to have a particular chemical property, or composition. Such tailoring permits the tip of the nanostructure to be functionalized in different ways.

#### Nanostructure

**[0093]** The nanostructures formed by the methods of the present invention are preferably made predominantly from carbon. However, other chemical compositions are consistent with the methods of the present invention and are further described herein.

**[0094]** Nanostructures as referred to herein, encompass, carbon nanotubes, nanotubes generally, carbon nanostructures, other related structures such as nanofibers, nanoropes, and nanowires, as those terms are understood in the art.

**[0095]** By carbon nanotube (CNT), is meant a hollow cylindrical molecular structure, composed principally of covalently bonded  $sp^2$ -hybridized carbon atoms in a continuous network of edge-fused 6-membered rings, and having a diameter of from about 0.5 to about 50 nm. Typically a nanotube is capped at one or both ends by a hemispherical carbon cap having fused 5-and 6-membered rings of carbon atoms, though the nanotubes of the present invention are not necessarily capped. Carbon nanotubes may be, in length, from a few nanometers, to tens or hundreds of microns, to several centimeters.

**[0096]** The typical make-up of a CNT is analogous to a sheet of graphitic carbon wrapped on itself to form a closed surface, without any dangling bonds. Thus, CNT's typically consist of a closed network of 6-membered carbon rings, fused together at their edges. Most CNT's have a chirality that can be envisaged as arising if a sheet of graphitic carbon is sheared slightly before it is bended

back on itself to form a tube. CNT's of any chirality may be formed by the present invention. It is also consistent with the present invention, however, that the carbon nanotubes also may have a number of 5-membered rings, fused amongst the 6-membered rings, as is found in, for example, the related "fullerene" molecules, and where necessary to, for example, relieve strain or introduce a kink. Carbon nanotubes have electrical properties that range from metallic to semiconductors, depending at least in part on their chirality.

**[0097]** By suitable choice of materials lying in between the substrate and the base of the nanostructure, and their sequence, the morphology of the nanostructure that is formed can be tailred. Such nanostructures include, but are not limited to, nanotubes, both single-walled and multi-walled, nanofibers, or a nanowire. Such tailoring can arise from, *e.g.*, the choice of texture of the catalyst layer that is positioned between the substrate and the nanostructure.

[0098] Carbon nanotubes made by the methods of the present invention may be of the single-walled variety (SWCNT's), having a cylinder formed from a single layer of carbon atoms such as a single layer of graphitic carbon, or of the multi-walled variety (MWCNT's), having two or more concentrically arranged sheaths of single layers. MWCNT's may consist of either concentric cylinders of SWCNT's or stacks of frusto-conical shaped single-walled structures.

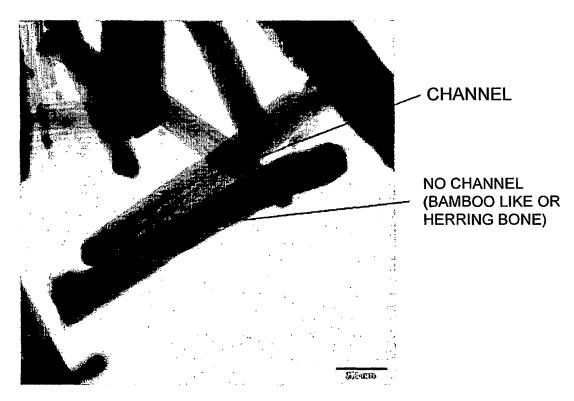

**[0099]** A carbon nanofiber (CNF) is typically not hollow, but has a "herring-bone" or "bamboo"-like structure in which discrete segments of carbon fuse together one after another. The typical diameters ranges from 5 nm to 100 nm. A conical segment of catalyst containing material is typically found at the tip of such a nanofiber. Carbon nanofibers are thus not crystalline and have different electrical conductivity from carbon nanotubes. Carbon nanofibers are effective interconnects in electronic circuits because they support electric current densities of around 10<sup>10</sup> A/cm<sup>2</sup>. Carbon nanofibers thus have a higher atomic density, given by numbers of carbon atoms per unit volume of fiber, than the, hollow, nanotubes.

**[0100]** Carbon nanofibers made according to the present invention also can be generally straight, and have a conical angle < 2°, see FIG. 1, where the conical angle definition assumes that the base of the nanostructure is broader than its tip. Since an angle  $\theta \approx \tan\theta$  when  $\theta$  is small, the conical angle  $\approx (w_{\rm b} - w_{\rm t})/2$  L, where  $w_{\rm b}$  and  $w_{\rm t}$  are the width of respectively the base and the tip of the nanostructure, and L is its length, measured along its axis.

**[0101]** A carbon nanorope has a diameter in the range 20-200 nm, and thus is typically larger in diameter than a carbon nanotube. A carbon nanorope is typically constructed by intertwining several nanotubes in a manner akin to the way in which a macroscopic rope consists of several strands of fiber bundled together. The various nanotubes in a nanorope may be twisted around one another or may line up substantially parallel to one an-

other; the individual nanotubes are held together principally by van der Waals forces. Such forces, although individually weaker than a covalent bond between a pair of atoms, are in the aggregate very strong when summed over all of the pairs of atoms in adjacent tubes

#### The Interface

**[0102]** According to the present invention, by suitable choice of materials and their sequence, the interface between the base of the nanostructure and the substrate can be chosen to have various electrical properties. For example, it can be chosen to be an ohmic contact, a Schottky barrier, or a controllable tunnel barrier.

**[0103]** An Ohmic contact is a metal-semiconductor contact with very low resistance, independent of applied voltage (and which may therefore be represented by a constant resistance). The current flowing through an ohmic contact is in direct proportion to an applied voltage across the contact as would be the case for an ohmic conductor such as a metal. To form an ohmic contact, the metal and semiconductor must be selected such that there is no potential barrier formed at the interface (or so that the potential barrier is so thin that charge carriers can readily tunnel through it).

**[0104]** A Schottky barrier is a semiconductor-metal interface in which the metal-semiconductor contact is used to form a potential barrier.

**[0105]** A tunnel barrier is a barrier through which a charge carrier, such as an electron or a hole, can tunnel. **[0106]** FIG. 2 is a flow-chart that describes in overview a process of making nanostructures on a substrate according to the present invention. First, one chooses a stack material, step 10. Then, a stack is created from the chosen materials, step 20, for example by deposition, sputtering or evaporation on to a substrate. Then, nanostructures are grown on the stack, step 30, for example in a growth/deposition chamber. Finally, the structure is incorporated into a device, by one or more additional fabrication techniques, step 40.

**[0107]** Chemical Vapor Deposition (CVD) is the preferred method for growth of nanostructures according to the present invention. However, there are different kinds of CVD methods that can be used, e.g., thermal CVD, PECVD, RPECVD, MOCVD (metallo-organic CVD), etc. It would be understood by one of ordinary skill in the art, that other variants of CVD are compatible with the present invention and that the practice of the present invention is not limited to those methods previously referenced

[0108] It is preferable that the substrate for use with the present invention is a conducting substrate. Accordingly, it is preferably a metal, or a metal alloy substrate. [0109] By the methods of the present invention, step 10 can influence the properties of the nanostructures that are grown. In particular, the nature and properties of the nanostructure are governed by the nature and extent of interdiffusion of the layers between the substrate and the nanostructure. Permitting interdiffusion can control the

diameter and morphology of the nanostructure, the number of nanotubes that grow per unit area of substrate, as well as the density of a nanostructure, and the electrical properties of the interface. On the other hand, using materials that impede diffusion between the substrate and the carbon nanostructure can control chemical interactions with the interface materials on both sides of the material, as well as the electrical properties of the interface.

[0110] The layers of materials in the stack can be deposited as a continuous film in the case where it is desired to grow many, e.g., an array of several hundreds or many thousands of, nanostructures on a single substrate. A patterned film can also be used to control the properties but in specific localized areas, leading to fabrication of individual devices. The deposited film thickness may vary from 0.5 nm to more than 100 nm, e.g., as much as 150 nm, 200nm, or even 500 nm, depending on the substrate underneath. Preferably, however, the thickness is from 1 to 10 nm, and even more preferably, from 5 to 50 nm. [0111] The nanostructures of the present invention can also be grown individually rather than as a dense "forest". For example, such nanostructures may be discrete carbon fibers. This is the case where catalyst layer and sizes are defined by lithography for example. For the case where a continuous film (in the form of stripes and squares larger than 100 nm X 100 nm) is used, more densely packed structures are possible (approximately 15 nm spacing between two adjacent nanostructures is preferred). In such continuous film configurations, the packing density and resulting diameter of the nanostructures can however be controlled by the choice of support layer.

**[0112]** In particular, the body of the nanostructures can be designed to be structures that include: hollow with electrical properties such as semiconducting or metallic; not hollow with different electrical properties (mainly metallic); hollow with different mechanical properties; and not hollow with different mechanical properties.

#### Controlling Nanostructure properties

[0113] The present invention encompasses nanostructures grown from substrates, and interface layers situated therebetween, having the following characteristics. The substrate is preferably a metal layer, which maybe disposed on a support. The support is typically a wafer of silicon or other semiconducting material, glass, or suitable flexible polymer used in thin film technology. The metal is preferably selected from the group consisting of molybdenum, tungsten, platinum, palladium, and tantalum. The thickness of the metal layer is preferably in the range 1 nm to 1 μm and even more preferably in the range 1 nm to 50 nm. The metal layer is preferably deposited by any one of several methods known in the art, including but not limited to: evaporative methods such as thermal or vacuum evaporation, molecular beam epitaxy, and electron-beam evaporation; glow-discharge

30

35

40

methods such as any of the several forms of sputtering known in the art, and plasma processes such as plasma-enhanced CVD; and chemical processes including gasphase processes such as chemical vapor deposition, and ion implantation, and liquid-phase processes such as electroplating, and liquid phase epitaxy. Examples of deposition technologies are found in Handbook of Thin Film Deposition, K. Seshan, Ed., Second Edition, (William Andrew, In., 2002).

**[0114]** The interface layers, also called intermediate layers or an intermediate layer, comprise one or more layers, in sequence, disposed upon the substrate. On top of the interface layers is a layer of catalyst. The nanostructure is grown from on top of the catalyst layer.

[0115] The interface layers may consist simply of a single layer of material. In this circumstance, the single layer is preferably silicon or germanium. The layers can be deposited in the form of amorphous or crystalline by techniques such as evaporation, or sputtering. The preferable thickness ranges from 1 nm to 1  $\mu m$  and even more preferably in the range 1 nm to 50 nm.

[0116] The interface layers may comprise several layers of different materials and may be, arbitrarily, classified according to function. For example, the layers in the vicinity of the substrate are characterized as layers that influence the electrical properties of the interface. The layers in the vicinity of the catalyst are characterized as layers that influence the composition and properties such as electrical/mechanical properties of the nanostructure. [0117] Various configurations of interface layers are compatible with the present invention. For example, a sequence of up to 3 layers may be deposited on the substrate, for the purpose of controlling the electrical properties of the interface. Such configurations include, but are not limited to: a sequence of insulator, conductor or semiconductor, and insulator; a sequence of insulator adjacent to the substrate, and a semiconducting layer; a sequence of semiconductor, insulator, semiconductor; a sequence of two insulating barrier layers adjacent to the substrate, and a semiconductor; a single layer of a metal that is different from the metal of the substrate; and a sequence of a metal that is different from the metal of the substrate, and a semiconducting layer. In such configurations, the insulator may be selected from the group consisting of:  $SiO_x$ ,  $Al_2O_3$ ,  $ZrO_x$ ,  $HfO_x$ ,  $SiN_x$ ,  $Al_2O_3$ , Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, and ITO. The semiconductor may be silicon or germanium. The metal, where present, may be palladium, platinum molybdenum or tungsten. Where two layers of the same character are present, e.g., two semiconducting layers, it is not necessary that the layers have the same composition as one another.

**[0118]** The uppermost layer of the foregoing interface layers may itself abut against the catalyst layer. This is particularly the case where the uppermost layer is a semiconductor such as silicon or germanium. However, it is additionally possible for the foregoing interface layers to have disposed upon them a further layer or sequence of layers that lies between them and the catalyst layer. Such

additional, or second, interface layers are thought of as controlling the properties and composition of the nanostructure. The second interface layers may be a pair of layers, such as a metal layer and on top thereof a semiconductor layer adjacent to the catalyst layer. Alternatively, the second interface layers may simply consist of a single layer of semiconductor. The metal layer, where present in the second interface layers, is preferably selected from the group consisting of tungsten, molybdenum, palladium, and platinum. The semiconducting layer in the second interface layers is preferably silicon or germanium.

**[0119]** The catalyst layer is typically a layer of metal or metal alloy, and may contain very fine particles of metal or metal alloy instead of being a continuous film. The catalyst layer preferably comprises a metal selected from the group consisting of nickel, palladium, iron, nickel-chromium alloy containing nickel and chromium in any proportions, and molybdenum.

[0120] The invention is primarily focused on a multistack configuration of at least one material layer between the catalyst layer and the conducting substrate, wherein the material is not of the same kind as the catalyst and conducting substrate, and wherein the material controls the chemical reactions between the various layers. Thus, the growth of the nanostructures on different conducting substrates can be controlled. Thereby the morphology and properties of the grown structures as well as the tip materials of the grown structures can be controlled. The current invention can be extended to having several stacks of materials of different kinds (semiconducting, ferroelectric, magnetic, etc.) which can be used to control the properties at base/interface, body and the tip of the nanostructure. It is also possible that the nanostructure is grown upon a conducting layer which is itself deposited on a substrate that itself can be of any kind, such as conducting, insulating or semiconducting.

**[0121]** High-k dielectric materials are mainly used as gate materials for CMOS devices. In the present invention such materials are utilized in part in multi-layer stacks to define the properties of the grown nanostructure as well as to control the interface properties between the nanostructure and the conducting layer.

**[0122]** According to the methods of the present invention, the presence of two or more intermediate layers will influence the texture/crystallographic structures of each other and the final catalyst particles.

**[0123]** Accordingly, the present invention preferably includes a conducting layer, at least one intermediate layer directly on the conducting layer, at least one catalyst layer directly on the intermediate layer, and a nanostructure on the catalyst layer.

**[0124]** The substrate may be a disposed on a support commonly used in semiconductor processing, such as a silicon wafer, or oxidized silicon wafer. The support may alternatively be a glass or metal or thin flexible polymer film used in the thin film technology as substrate.

[0125] It is to be understood that the at least one inter-

20

25

35

40

mediate layer is chosen to control various electrical properties of the interface between the substrate and the carbon nanostructure.

**[0126]** It is further to be understood that the choice of at least one catalyst layer controls various properties of the carbon nanostructure.

**[0127]** The grown nanostructures are preferably carbon-based materials such as carbon nanotubes (CNT), and carbon nanofibers (CNF). Carbon nanostructures form when the entire structure is placed in a mixture of carbon-containing gases. Preferred gases are hydrocarbons such as  $CH_4$ ,  $C_2H_2$  and  $C_2H_4$ , and generally aliphatic hydrocarbons having 5 or fewer carbon atoms, of any level of saturation.

**[0128]** The nanostructures can also be of different semiconducting materials referred to as III-V, or II-VI materials, such as InP, GaAs, AlGaAs, depending on the choice of catalyst and subsequent chemical chamber conditions used.. Keeping all the other materials stack same as for a carbon nanostructure described herein, simply changing the catalyst type and or composition of gases can facilitate growth of these non-carbon nanostructures. Therefore without deviating from the other aspects of the invention described herein, a person of ordinary skill in the art can grow different kinds of solid state nanostructures. Examples of conditions for forming such nanostructures are as follows.

**[0129]** SiC nanostructures: chambers - MOCVD (metallo organic CVD); gas composition-dichloromethylvinylsilane [CH $_2$ CHSi(CH $_3$ )Cl $_2$ ]; catalyst-Ni; and temperature: 800-1200 °C.

**[0130]** Si nanostructures: chamber type - vapor-liquid-solid (VLS)/CVD; gas composition-SiH $_4$ , Si $_2$ H $_6$ ; catalyst-Ni; and temperature 500 - 1000 °C.

**[0131]** InP/GaP nanostructures: chambers - MOCVD/CVD; gas composition- elemental indium and gallium with triphenyl phosphine, trimethyl-gallium and  $N_2$ ; catalyst; and temperature: 350-800 °C.

**[0132]** GaN nanostructures: chambers - MOCVD (metallo organic CVD); gas/ composition-elemental gallium and ammonia gas; catalyst- Ni; and temperature: 800 - 900 °C.

**[0133]** ZnO nanostructures: chambers - MOCVD/CVD; gas composition - oxidation of Zinc carrying elements; catalyst-Ni; temperature 30 - 700 °C.

**[0134]** The grown nanostructures for materials other than carbon can be of the form of forests consisting of uniform structures covering the substrate area and/or arrays, or individual structures.

**[0135]** The choice of catalyst plays an important role because the growth of carbon nanostructures is ordinarily catalytically controlled. Since the crystallographic orientation of the catalysts partakes in defining the morphology of the nanostructure, it is expected to obtain different growth mechanisms from different types of catalysts. Besides catalyst crystallographic orientation, there are many other growth conditions that influence the structure formation, such as the mixture of gases, current density

for the case when plasma density is controlled, voltage between the cathode and anode, temperature of the substrate, chamber pressure, etc. (see, *e.g.*, Kabir, M. S.; Morjan, R. E.; Nerushev, O. A.; Lundgren, P.; Bengtsson, S.; Enokson, P.; and Campbell, E. E. B., Nanotechnology 2005, (4), 458)).

**[0136]** FIGs. 3A and 3B show an overview of various structures according to the invention. FIG. 3A shows how a carbon nanostructure having a tip 110, body 120 and a base 130, and made by processes described herein, can be positioned vertically on a metal substrate as in the left-hand side of FIG. 3A, or horizontally on an insulating substrate as in the right-hand side of FIG. 3A. Positioning on an insulating substrate will allow for further processing for making functional devices. The bottom substrate (not shown) underneath the insulating layer can be used as a bottom gate dielectric and the substrate underneath the oxide as bottom gate electrode to *e.g.*, modulate the resistance of a semiconducting nanostructure. See FIG. 3B.

**[0137]** FIG. 3B shows various configurations of one or more intermediate layers 210 between a conducting substrate 200 and a catalyst layer 220. The invention proposes a platform comprising at least one material stack (denoted, e.g., layer 1) between the catalyst layer and the conducting substrate. The purpose of the multiple materials stacks (denoted, e.g., layer 1, layer 2, ...layer n) is to control the interface properties between the conducting substrate and the grown nanostructures (for example, ranging from Ohmic contact to Schottky barrier), the properties of the grown nanostructures (morphology, mechanical, and electrical properties), and the properties of the tip 110 of the grown nanostructures.

**[0138]** FIGs. 5 and 6 show embodiments of a device having a single intermediate layer. In FIG. 5, in another embodiment, a metal layer 510 is on a wafer 520; an intermediate layer of silicon 530 is on the metal layer; and a catalyst layer 540, typically Ni, or Fe, or others such as NiCr or, Pd, is on the intermediate layer. Together, layers 530 and 540 are referred to as the interface.

**[0139]** In FIG. 6, another typical individual nanostructure is shown. In this structure, a metal layer 610 is on a wafer 620; an interface 630 between the metal layer and a body of a nanostructure 640 is formed from an intermediate layer of semi-conducting material 645 such as silicon. The tip 650 of the nanostructure contains a mixture of materials, including principally catalyst that has diffused up the body of the nanostructure as the nanostructure has grown, and also some metal.

**[0140]** FIG. 4 shows a representative embodiment having a multilayer stack supporting a partially formed nanostructure 499. A metal layer 410 acts as a substrate, and is disposed on a support 420, e.g., a wafer of silicon. A 3-layer stack acts as an intermediate layer between the metal substrate and a second stack of catalytic layers and controls the electrical properties of the interface. The intermediate layer has, in order, starting with a layer in contact with the metal: a first control layer 430, of e.g.,

25

30

35

40

45

50

55

SiO<sub>x</sub>, or Al<sub>2</sub>O<sub>3</sub>; on top of the first control layer is a metal/ semi-metal layer 440, e.g., Ge; on top of the metal/semimetal layer is a second control layer 450 of, e.g., ZrO<sub>x</sub> or  $HfO_x$  or any other material with high k dielectric value such as SiN<sub>x</sub>, Ta<sub>2</sub>O<sub>5</sub>, Al<sub>2</sub>O<sub>3</sub>, and TiO<sub>2</sub>. The subscript 'x' in a chemical formula denotes a variable stoichiometry, usually controllably variable. The two control layers control diffusion from respectively the metal/semi-metal layer into the substrate and into the catalyst stack The thickness and composition of the two control layers provide two variables with which such control may be achieved. The thickness for a single layer ranges from less than 10 nm to several hundreds of nanometer and the thickness of the total material stack ranges from less than 10 nm up to microns and above. Together, the first control, metal/semi-metal, and second control layers permit control of electrical properties of the interface between the metal and the carbon nanostructure. To obtain different electron/hole tunneling properties, it is a matter of choosing different oxides to give a variation of electrical tunneling properties and hence varying electrical properties of the interface between the nanostructure and the base substrate 410. Principally, such choices are determined by the dielectric constant of the control layer materials such as oxides.

**[0141]** Also referring to FIG. 4, a multilayer stack disposed on the second control layer controls properties of the carbon nanostructure that grows above it. In the example shown, adjacent to the second control layer is a first metal layer 460, e.g., tungsten, molybdenum, palladium, platinum; adjacent to the first metal layer is a silicon layer 470; and on top of the silicon layer is a second metal layer 480 composed of, e.g., nickel or palladium.

[0142] FIG. 7 shows another embodiment of a nanostructure having a tip 610, a body 620, and an interface 630. A metal layer 640 is disposed on a wafer 650 and consists of a metal selected from the group consisting of molybdenum, tungsten, platinum, tantalum, and palladium. A two-layer interface 630 is on the metal layer 640 and has a first intermediate layer 660 of oxide, such as SiO<sub>x</sub>, ZrO<sub>x</sub>, HfO<sub>x</sub>, or TiO<sub>x</sub>; a second intermediate layer 670, composed of silicon, is disposed on the first intermediate layer and is in contact with the body of the nanostructure. The tip 610 of the nanostructure contains Ni, Fe, Mo, or Pd, or an alloy such as NiCr or a mixture of the materials found in the material stack. The metal content of the tip originates with a layer of catalyst (not shown in FIG. 7) that was situated between the uppermost intermediate layer and the bottom of the nanostructure.

**[0143]** FIG. 8 shows another nanostructure having a tip 710, a body 720, and an interface 730 which comprises a multi-layer stack. A metal layer 740 is disposed on a wafer 750. A three-layer interface 730 is on the metal layer 740 and has a first intermediate layer 760 of semimetal such as germanium; a second intermediate layer 770 of oxide, such as SiO<sub>x</sub>, ZrO<sub>x</sub>, HfO<sub>x</sub>, or TiO<sub>x</sub>; and a third intermediate layer 780, composed of silicon, which

is in contact with the body of the nanostructure. The tip of the nanostructure contains Ni, Fe, Mo, or Pd, or an alloy such as NiCr or a mixture of the materials found in the interface.

[0144] FIG. 9 shows another embodiment of a nanostructure: a metal layer 910 is disposed on a wafer 920; an interface 930 having three intermediate layers is disposed on the metal layer 910. The three intermediate layers, in sequence moving away from the metal, are: a second barrier layer 940, a first barrier layer 950 and a semiconducting layer 960, in contact with the body of the nanostructure 970. The first barrier layer can be used as a material diffusion barrier upwards/downwards, and the second barrier layer can be used as defining the electrical tunnel barrier. The body of the nanostructure can have electrical properties either as a semiconductor or a conductor. The tip 980 of the nanostructure contains catalyst. [0145] As is seen from FIGs. 6-9, catalyst diffuses into the body of the nanostructure during growth initiation. This process is described in further detail in FIG. 10. In FIG. 10, a metal underlayer 1010 of a metal such as W, Mo, Pt, Pd,. is on a wafer 1020. An intermediate layer of a semiconducting material 1030 such as silicon or germanium, or a compound of III-V elements from the periodic table, is on the metal underlayer. A catalyst layer 1040 having a metal such as Ni, Fe, Co, or an alloy such as NiCr is on the intermediate layer.

**[0146]** A stage during growth of the nanostructure is shown in the right-hand panel of FIG. 10. An expanded view of the metal underlayer is shown. An interface 1060 between the metal underlayer and the body 1050 of the growing nanostructure contains an alloy of catalyst with metal underlayer, metal silicides, and the metal underlayer itself.

**[0147]** The intermediate layer 1030 is used to start the growth process. However it diffuses into the metal underlayers creating metal compounds such as metal-silicides if the intermediate layer is silicon, which function as Ohmic contacts with the metal underlayer. Accordingly the nanostructure is grown by direct contact with metal underlayer where no intermediate layer is present in between the initial catalyst and metal underlayer. A small portion of catalyst is present at the bottom. The tip consists of catalyst rich metal underlayer: a large portion of catalyst is present at the tip of the nanostructure together with a small portion of metal underlayer.

[0148] In FIG. 11, an embodiment of nanostructure growth uses a tungsten (W) metal underlayer 1110 on a wafer 1120. A stack having a layer of silicon 1130 on top of the metal underlayer, and a layer of nickel 1140 on top of the silicon is in contact with a growing nanostructure 1180. The material stack conditions before growth (FIG. 11, left hand panel) show discrete layers. The material stack conditions after growth (FIG. 11, right hand panel) show that interdiffusion amongst the layers has occurred: there are now distinct regions of nickel-tungsten alloy 1150, tungsten-silicon alloy 1160, and undiffused tungsten 1170. It is also consistent with the conditions that

35

40

45

the regions of, e.g., nickel and tungsten have a gradation of properties without a discontinuity in the concentrations of the respective metals or a sharp concentration gradient.

[0149] FIG. 12 shows a multilayer stack between a metal underlayer 1210 and a nanostructure body 1230. The multilayer stack comprises two interfaces, a first interface 1240 to control electrical properties of the interface, and a second interface 1250 to control physical properties of the nanostructure body. Metal underlayer 1210 is on a wafer 1220. First interface 1240 comprises two layers disposed on the metal control the electrical properties of the interface. A layer of germanium 1260 is directly on the metal 1210, and a layer 1270 of an oxide such as SiO<sub>x</sub>, ZrO<sub>x</sub>, HfO<sub>x</sub>, or TiO<sub>x</sub> is directly on the germanium. The oxide layer acts as a buffer. Two further layers, disposed on the oxide layer, serve to control physical properties of the body of the nanostructure. A first layer 1280 of silicon is directly on the oxide layer, and a layer 1290 of metal catalyst such as nickel, iron, or palladium is in between the silicon layer and the body of the nanostructure.

#### Process for forming nanostructures

**[0150]** The present invention further comprises a process for forming nanostructures. The process comprises first depositing an electrode on a substrate. The substrate, as further described herein, may be a wafer of silicon, and preferably has an insulating coating, such as an oxide, for example SiO<sub>2</sub>. The electrode functions as an underlayer for the nanostructure, and is made of a conducting material, preferably a metal such as molybdenum, niobium, or tungsten. The method of depositing the electrode can be any one familiar to one of ordinary skill in the art, but is preferably a method such as electron beam evaporation. The electrode layer is between 10 and 100 nm thick, and is preferably 50 nm thick.

**[0151]** Optionally, a resist is then deposited on the electrode layer. Such a resist is usually used for technologies that utilize lift-off processes for metal depositions. An exemplary resist is a double-layer resist consisting of 10% co-polymer and 2% PMMA resist, that is applied by consecutive spin coating and baking. The resist is then patterned/exposed by a radiation source, such as UV light or an electron beam, to transfer the design into the resist layer.

**[0152]** A catalyst layer, either as a sheet or as dots, is fabricated on the metal substrate or on the resist, where present. Dots of catalyst facilitate controlled growth of individual nanostructures in precise locations. Catalyst dots may be constructed by electron beam lithography. Their dimensions can be controlled using the shot modulation technique. With this technique, catalyst dot sizes can be determined with nanometer precision, and dots as small as 5-10 nm in dimension can be formed. The catalyst layer is not heated during this stage.

[0153] On the catalyst layer, layers of other materials

are deposited. Such layers include at least one layer of semiconducting material and may include at least one layer of a metal different from the metal of the underlying electrode. The semiconducting material is preferably deposited using an electron beam evaporator. The semiconducting material is preferably amorphous silicon, and the layer has a thickness of 5 - 100 nm, preferably 10 nm. [0154] After the various layers, including one layer of semiconducting material, are deposited a layer of catalyst material is deposited, thereby forming an uppermost layer upon which nanostructures are ultimately fabricated. The catalyst layer is deposited by standard techniques known in the art such as electron beam evaporation or sputtering.

**[0155]** Optionally, if a resist has been applied, it can now be removed by a lift-off process, for example by washing the structures in acetone at 60 °C, followed by washing with iso-propyl alcohol. After these washings, the structures are rinsed in deionized water and blowdried with nitrogen gas.

[0156] Nanostructures can now be grown upon the remaining areas where catalyst layers are exposed. The preferred technique for effecting such growth is plasmaenhanced chemical vapor deposition. As previously described herein, the composition of the vapor will determine the types of nanostructures that are grown. For example, carbon nanotubes can be grown at 5 mbar pressure in a (1:5) mixture of C<sub>2</sub>H<sub>2</sub>:NH<sub>3</sub> gas. Growth of nanostructures typically occurs at high temperatures, in the range 600 -1,000 °C, such as 700 °C. The substrate (with electrode, semiconducting material, and catalyst layers thereon) are brought up to such high temperatures by ramping the temperature up relatively rapidly. Exemplary rates are from 1-10 °C/s, preferred rates being in the range 3 - 6 °C/s. Such conditions have been referred to in the art as 'annealing', and preferably occur in a vacuum. A low vacuum (e.g., 0.05 - 0.5 mbar pressure) suffices. The source gases for the nanostructures are introduced into the chamber when the maximum temperature is reached.

**[0157]** The nanostructures are typically cooled to room temperature before they are permitted to be exposed to air

**[0158]** Control over individual nanostructure formation is thus achieved because specifically tailored catalyst dots are created, rather than relying on non-uniform break up of a layer of catalyst by prolonged heating prior to nanostructure formation.

#### Applications

**[0159]** Applications of carbon nanostructures made by the methods described herein include: construction of composites for use in structural engineering, as well as structures having high strength but light mass, as might be used for objects sent into outer space; electrochemical devices and sensors for diagnostics, as are used in the life sciences; research tools such as electron emitters,

20

25

40

45

50

small size X-ray generators, and atomic force microscopy probes; and applications to circuitry components used in electronics such as interconnects, diodes, heat dissipative media, high frequency filters, optical devices such as light emitting diodes, wave guides, opto-electronic circuits, hydrogen storage devices, qubits for quantum computing, and super capacitors.

[0160] For example, FIG. 12 shows how an individual nanostructure can become part of an electric circuit. A 3-layer stack 1310 controls properties of the interface and consists of a first diffusion barrier 1330, adjacent the metal 1320, and composed of  $SiO_x$  or  $Al_2O_3$  or another dielectric material. An island 1340, of metal or semi-metal is situated between the first diffusion barrier and a second diffusion barrier 1350 of ZrO<sub>x</sub> or HfO<sub>x</sub> or choice of other dielectric material. A further 3-layer stack 1360 controls properties of the interface and is on the second diffusion barrier layer 1350. A metal layer 1370 acts as a growth substrate to control the properties of the grown structures and is in contact with the second diffusion barrier 1350; a silicon layer 1380 is on the metal layer and a nickel or palladium catalyst layer 1390 is on the silicon layer. The silicon layer allows interdiffusion to control the properties of the grown structures. The carbon nanostructure 1395 is conductive in this example and is a carbon nanofiber. Metal layer 1320 is on a wafer 1305.

**[0161]** FIG. 14 shows how the nanostructure of FIG. 13 would function in an electric circuit that contains a battery 1410 as a representative voltage source. The items labeled 1330, 1340, 1350, and 1395 in FIG. 14 correspond to similarly numbered items in FIG. 13.

[0162] FIG. 15 shows how an individual nanostructure can form part of an electronic device. The metal underlying layer 1510, is disposed on wafer 1520, and is for example tungsten and is a first instance of a first metal. A second metal, having a different work function from the underlying metal, for example is platinum, forms a layer 1530 disposed on the underlying metal layer. This second metal layer controls the electrical properties of the interface between metal layer 1510 and the carbon nanostructure 1540. A second layer 1550 of the first metal is disposed on the layer of second metal. This layer and the two above it control the properties of the nanostructure. The two layers above layer 1550 are, in sequence, silicon 1560 , and iron 1570. The last of these is a catalytic layer. In this embodiment, the carbon nanostructure is a semiconductive carbon nanotube.

**[0163]** FIG. 16 shows how a nanostructure can form part of an electro-optical device such as a light emitting diode, or as the variable conducting channel like a transistor. A structure as in FIG. 15 is encapsulated in an insulator 1610 such as  $\mathrm{SiO}_{\mathrm{X}}$  on each side, and on top a third metal 1620, such as tungsten or calcium, having a different work function than that of the bottom metal electrode 1630 in the figure. Metal layer 1510 is disposed in a wafer 1630. Carbon nanostructure 1540 is a semiconducting carbon nanotube in this example.

[0164] FIG. 17 shows how an individual nanostructure

can form a Schottky barrier as part of an electrical device. A metal underlayer 1710 is disposed on a wafer 1720. On top of the metal underlayer 1710, which is composed of, e.g., tungsten, is a pair of layers that controls the electrical properties of the interface. A layer 1720 of a second metal, such as platinum, having a different work function from the metal of the metal underlayer 1710 is on top of the metal underlayer. A layer 1730 of a semiconductor such as germanium is on the layer of second metal. This combination of two metal layers and a semiconducting layer creates a Schottky barrier due to the mismatch of work function of different materials and therefore controls the electrical properties of the interface. Three further layers for controlling the properties of the nanostructure above, are disposed upon the semiconductor layer 1730. In sequence, the three layers are: a layer 1750 of the first metal (in this instance tungsten), a silicon layer 1760, and lastly a nickel layer 1770 that functions as a catalyst. Disposed on the catalyst layer is a nanostructure such as a carbon nanotube or a carbon nanofiber.

[0165] FIG. 18 shows how an individual nanostructure can form a Schottky barrier as part of an electronic device. In this embodiment the lower segment, mentioned in the foregoing paragraph in connection with FIG. 17, and consisting of a metal and semiconductor layer, is excluded. The remaining segment consisting of material layers determining that the nanostructure has semiconducting properties is present: a metal layer 1820 is disposed on a metal underlayer 1810. The work function of the metal of layer 1820 is different from that for the metal underlayer 1810. On layer 1820 are, in sequence, a semiconductor layer 1830, of e.g., silicon, and a catalyst layer 1840 of e.g., iron. This embodiment consists of a semiconducting nanostructure 1850 grown on metal underlayer will create a Schottky barrier due to mismatch of work function of the metal and the band gap of semiconducting nanostructure. FIG. 19 shows a schematic representation of Schottky Barrier formation between the contact metal and the nanotube for a device as shown in FIG. 18, according to two types of metal electrodes: (a) for a large work function metal, and (b) for small work function metal. In the former case, the Fermi level E<sub>F</sub> of the electrode metal is close in energy to the valence band E<sub>V</sub> of the carbon nanostructure (denoted SWCNT), and holes pass easily across the interface from the metal to the carbon nanostructure. In the latter case, the Fermi level of the electrode metal is close to the conduction band E<sub>C</sub> of the carbon nanostructure, and electrons pass easily across the interface from the metal to the carbon nanostructure.

## Field emission device

**[0166]** In particular, the nanostructures of the present invention may form the basis of a field emission device. FIGs. 20A-20C show successively detailed views of such a device 2000. FIG. 20A shows, schematically, a field emission device having several pixels mounted in a

40

45

colors, red, green, and blue, and is independently ad-

chamber 2010. Each pixel has a metal substrate 2020, one or more nanostructures 2080 mounted thereon. The metal substrate is in electrical communication with a metal cathode 2060 through one or more interconnects 2070. Cathode 2060 is in electrical communication with a device controller 2050 and an anode 2040. Device controller is typically an electrical component capable of providing a voltage across a specific pixel. Device controller is preferably able to control multiplexing of the device so that pixels can be individually addressed, for example by using an active addressing scheme. In normal operation, upon application of a voltage between the cathode and anode, nanostructures 2080 emit electrons towards anode 2040. The electrons impact a phosphor layer 2030 that is in contact with the anode, and cause it to emit one or more photons of visible light. It is preferable that anode 2040 is transparent so that the photons are emitted in a direction away from the pixels. Chamber 2010 is preferably sealed so that it contains either a vacuum or an inert gas such as argon. This arrangement ensures that the nanostructures have a long lifetime and do not decompose or react with oxygen or water vapor normally found in air.

**[0167]** The system depicted in FIG. 20A is more practical than cathode ray tubes used in the art because it can be flatter. It also offers brighter displays than other comparable displays used in the art, such as LED's, OLED's, and LCD's. For example, the contrast ratios achievable with LCD's are around 1,000: 1, whereas those obtained from electron emission devices are around 20,000: 1. Such contrast ratios make electron emitting devices such as shown in FIG. 20A suitable for handheld devices such as cell-phones, GPS receivers, and other devices that see a lot of use in outdoor lighting conditions.