Sign up for our newsletter!

Your data will be handled in compliance with our privacy policy.

Your data will be handled in compliance with our privacy policy.

Research paper published in the proceedings of 2nd PCNS Passive Components Networking Symposium, Bucharest, Romania, 10–13 September, 2019. Award for outstanding paper.

R Andersson, M Bylund, S Krause, A M Saleem, V Desmaris • October 26, 2019

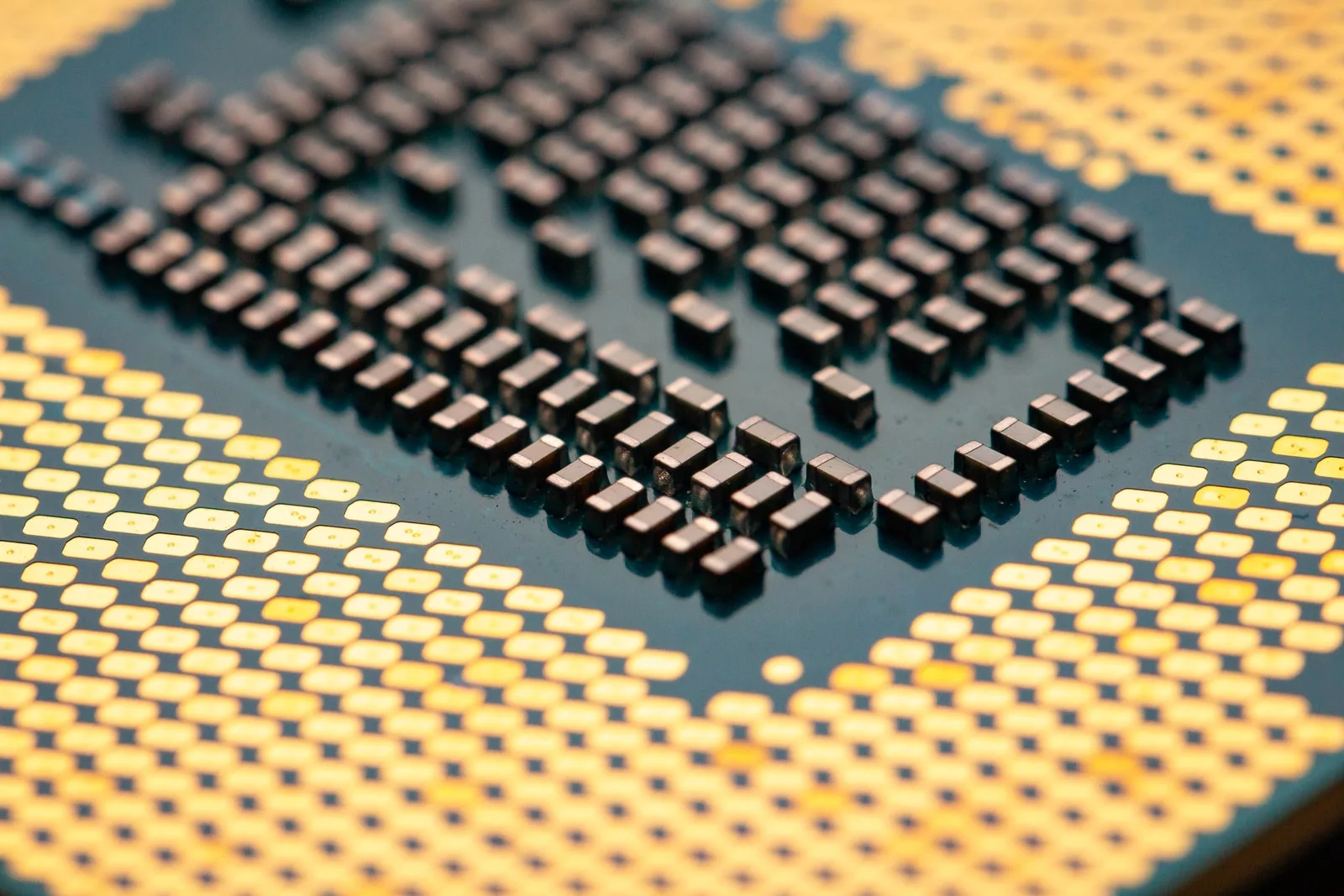

Complete on-chip fully solid-state 3D integrated capacitors using vertically aligned carbon nanofibers as electrodes to provide a large 3D surface in a MIM configuration have been manufactured and characterized. The capacitance per device footprint area has been studied, as well as its behavior at different temperatures and frequencies. Equivalent series resistance (ESR), breakdown voltage and leakage current have also been measured. The entire manufacturing process of the capacitors is completely CMOS compatible, and in combination with the low device profile of about 4 µm this makes the devices readily available for integration on a CMOS-chip, in 3D stacking, or redistribution layers in a 2.5D interposer technology. Capacitances of ca 350 nF/mm2, ESR of about 100 mΩ, breakdown voltages of up to 25 V and leakage currents in the order of 0.004 nA/nF have been measured.

Your data will be handled in compliance with our privacy policy.