Sign up for our newsletter!

Your data will be handled in compliance with our privacy policy.

Your data will be handled in compliance with our privacy policy.

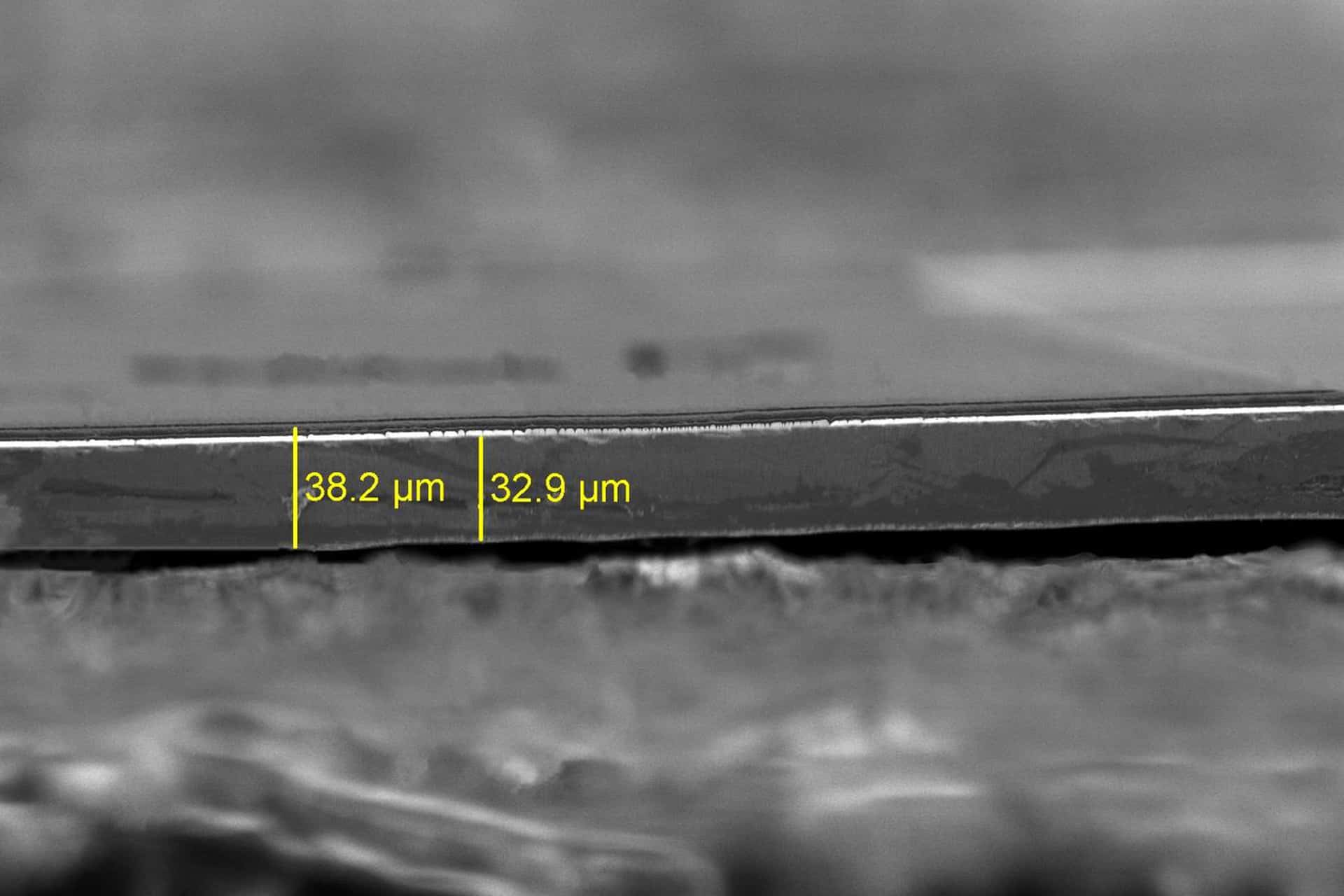

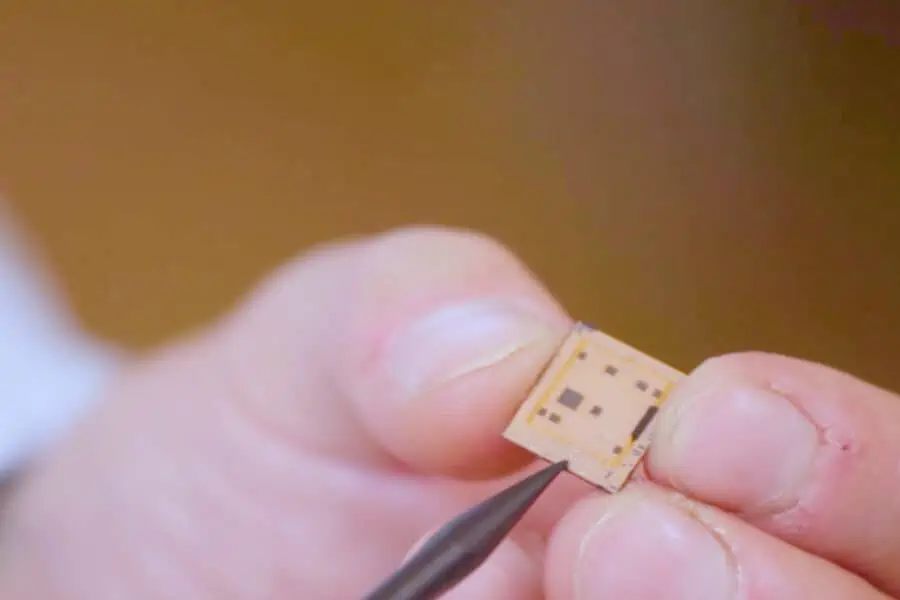

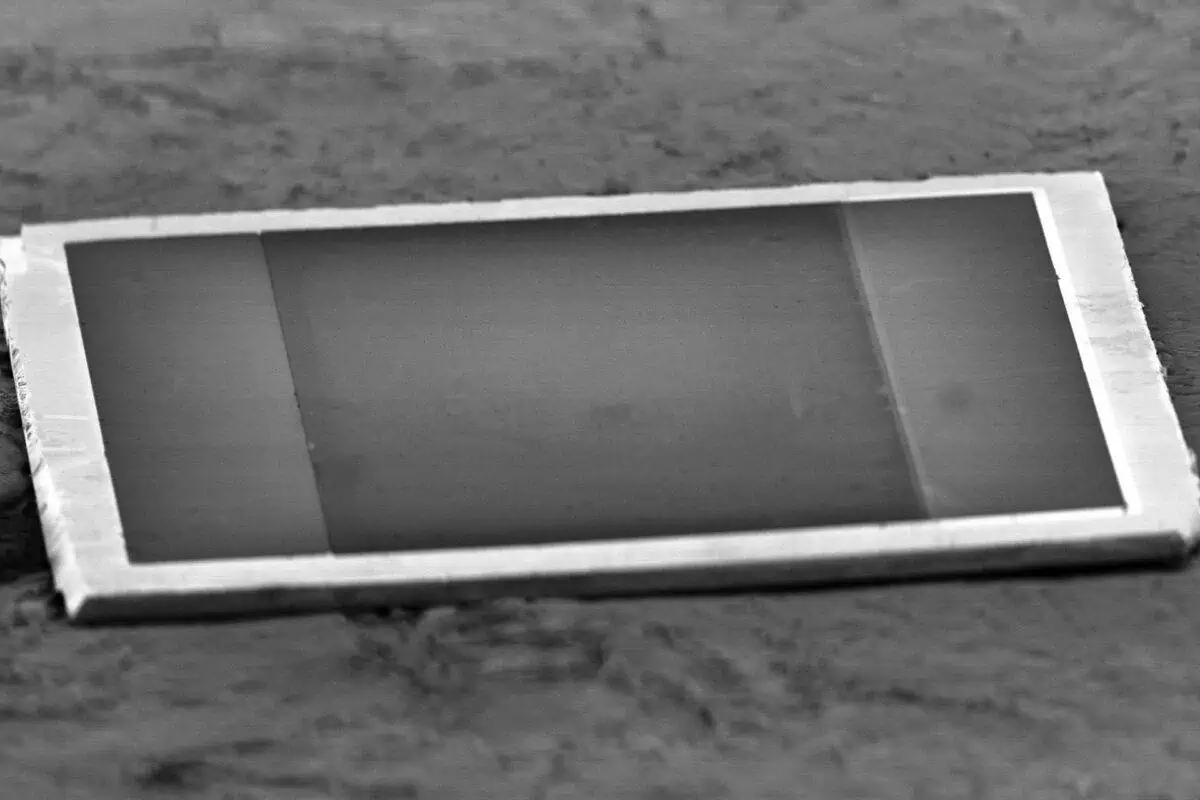

Smoltek has developed a prototype of the thinnest discrete capacitor in the world. Its total building height is less than 40 micrometers (38.2 µm to be exact). You have to stack a bunch of them on top of each other to reach the same height as today’s industry-standard regarding surface-mounted discrete capacitors. The capacitor, without encapsulation and substrate, is merely 0.5 to 10 µm in height. It can be built directly onto an integrated circuit’s die or built into its interposer.

The most amazing thing about this microscopic capacitor is its performance. One square millimeter has a capacitance of a whopping 650 nanofarads (650 nF/mm2). Its internal resistance (ESR) is less than forty milliohms (40 mΩ), and its internal inductance (ESL) is below fifteen picohenry (15 pH).

We describe our capacitor as a CNF-MIM capacitor since it is a metal-insulator-metal (MIM) capacitor where carbon nanofibers (CNF) are used to create a much larger surface area, hence higher capacitance than the form factor suggests.

We are developing ultra-thin and high-performance nanofiber-based capacitors for mobile application processors. The driving voltage decreases in today’s processors because more and more transistors can fit on a given surface. The lower drive voltage makes the processors increasingly sensitive to interference, and a number of so-called decoupling capacitors are required to stabilize the power supply.

To increase performance and reduce power consumption, these capacitors must be placed as close to the processor chip as possible. For the capacitors to be placed as close to the processor chip as possible, they must be extremely thin. They must also be high-performance, i.e. stable at high frequencies and with low internal losses.

Our carbon nanotechnology makes it possible to manufacture capacitors with a unique combination of superior electrical performance at very high frequencies and an extremely small form factor—ultra-thin capacitors.

Smoltek’s upcoming product family for decoupling capacitors for the semiconductor industry is intended to be placed in the application processor chip.

A discrete CNF-MIM capacitor has a smaller footprint (area) and much thinner profile (z‑dimension) than any other capacitor with the same capacitance. CNF-MIM capacitors up to more than 650 nF can be made less than 40 µm in height. The actual form factor can be varied according to the design and need.

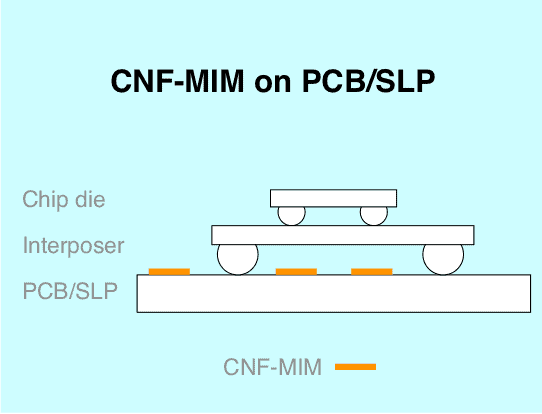

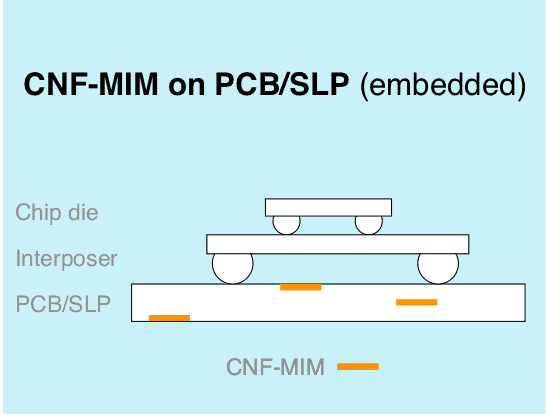

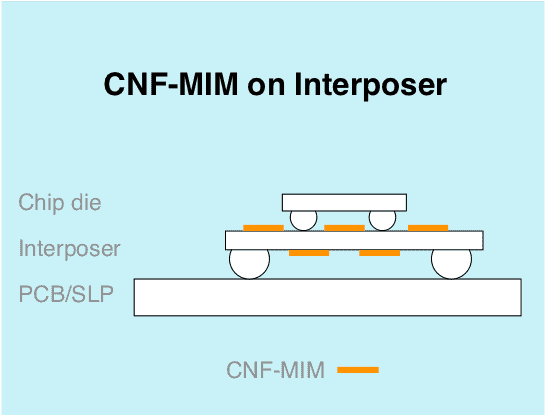

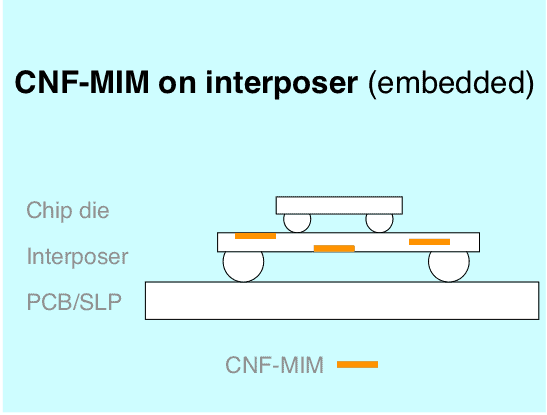

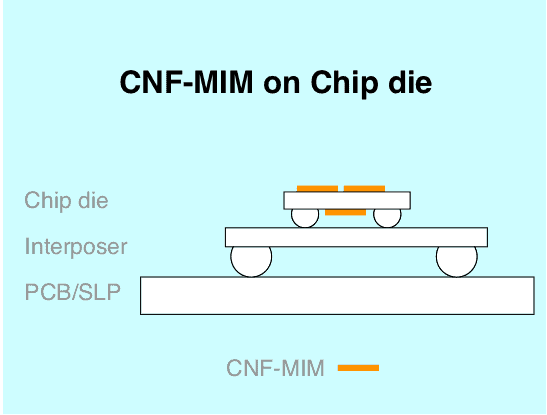

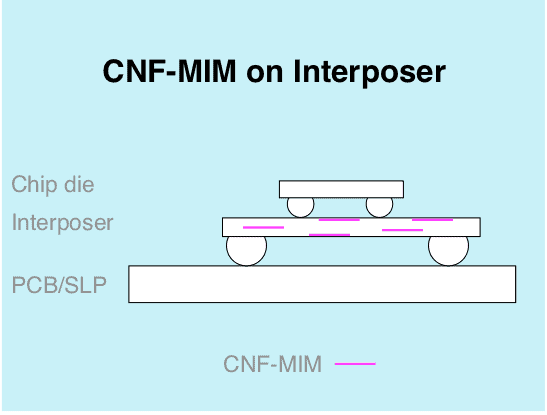

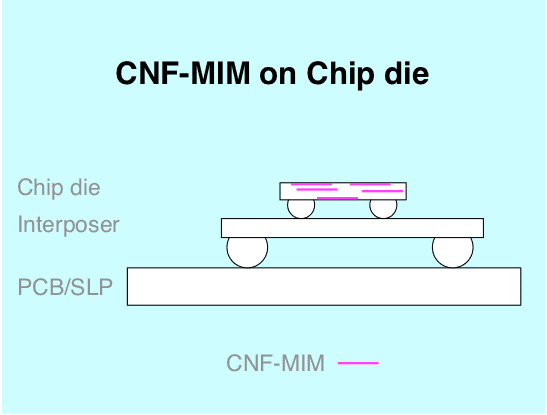

As shown in the illustrations, a discrete CNF-MIM capacitor can be

A CNF-MIM capacitor can also be integrated directly into chip die or chip interposer. The height of the integrated capacitors is a mere 0.5 to 10 µm. The benefits of integrated CNF-MIM are many:

As shown in the illustrations, a CNF-MIM capacitor can be

Multilayer Ceramic Capacitors (MLCC) form the industry standard for surface-mounted device (SMD) capacitors. Every year, trillions of MLCCs are built into electronic devices. They are 300 µm high. CNF-MIM offers the same capacitance at a tenth of that height.

The miniaturization of electronics is creating a growing need for ever-smaller capacitors. And some circuits (such as Apple’s) use capacitors that are state of the art. These use improvements of MLCC and Low Inductance Chip Capacitors (LICCs) and Trench Silicon Capacitors (TSCs), all of which have a height of 80–100 µm.

However, MLCC, LICC, and TSC struggle to go down in height due to materials involved, processing schemes, and the cost of raw materials and processing. At the same time, SiP and SoC continue to become more compact. There is less and less space between interconnects (bumps), and they are getting shorter. To fit capacitors between the bumps, the capacitors must have a smaller footprint and, above all, be shorter—preferably less than 20 µm.

This is the problem that CNF-MIM capacitors solve. They have a much smaller footprint and, above all, a much lower height.

To create a capacitor with a minimal footprint and height, we use carbon nanofibers (CNFs) to multiply the contact area between the two metals and the intermediary dielectric.

Consider a single CNF with a diameter of 10 nm and a length of 5 µm. Its mantle surface is 2,000 times larger than the area it occupies. Thus, a forest of such CNFs would multiply the surface, but not by as much as 2,000. We can’t cover the entire original surface with CNFs; there must be space between them to allow access to the contact surface. But if the forest of CNFs covers about half the surface, then the surface multiplication would be in the range of 1,000 times.

CNF has many metallic properties, including being a good conductor of current. Therefore a metal plate covered to fifty percent by CNFs is a single electrode with a surface area about 1,000 times larger than the area of the metal plate itself. A MIM capacitor is obtained by coating this electrode with a uniformly thick layer of a dielectric and then coating this in turn with a metal. Of course, the dielectric should have a high relative permittivity to maximize the capacitance.

Since the CNF has a length much larger than the diameter, we can neglect what happens to the electric field near the base and top of each CNF. Essentially it will be a uniform field, just as in a parallel plate capacitor.

Since the capacitance of a parallel plate capacitor is directly proportional to the surface area, we conclude that CNFs have increased the capacitance density by 1,000 times.

But it doesn’t end there. If the second layer of metal is made uniformly thick, both sides of it will have the same shape as the first electrode. So another MIM capacitor is obtained by coating it with another dielectric layer and then coating it with metal. It will have the same capacity as the first. And by electrically connecting the first and the third metal layer, we achieve a parallel connection, which doubles the capacitance. This can be repeated as long as desired, and there is space between the carbon nanofibers. The last layer of metal does not need to be uniformly thick but can fill any remaining spaces between the carbon nanofibers.

Don’t hesitate to contact us with your questions.