Sign up for our newsletter!

Your data will be handled in compliance with our privacy policy.

Your data will be handled in compliance with our privacy policy.

Research

August 26, 2019

Research paper published in the proceedings of 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), 2019, pp. 1870-1876.

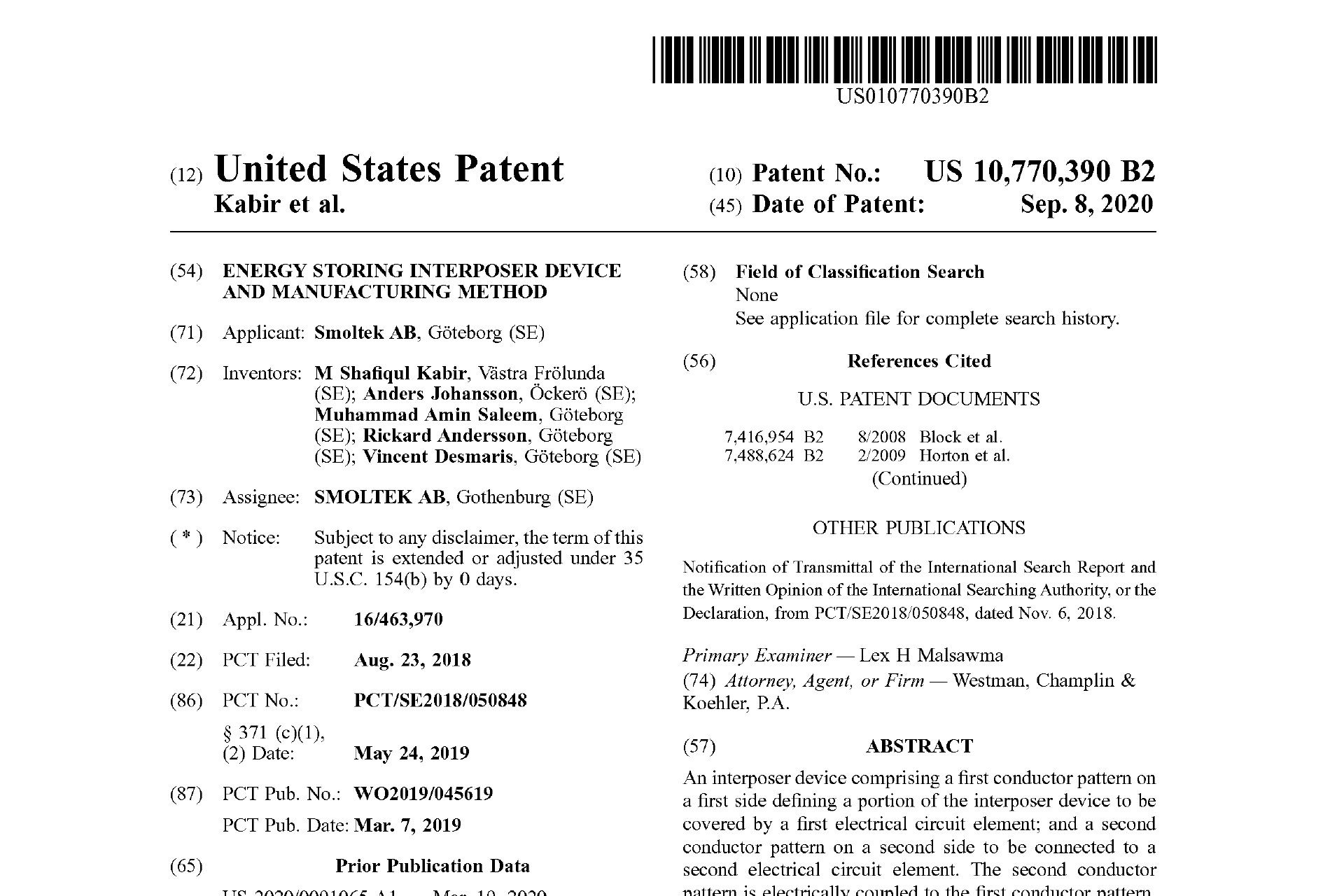

Patents

August 23, 2018

The Compact Energy Storage Interposer family is covering the invention and manufacturing of extremely thin energy storage devices embedded in an interposer.

Research

August 9, 2018

Research paper published in the proceedings of 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018, pp. 1382–1388.

Research

August 9, 2018

Research paper published in the proceedings of 2018 IEEE 13th Nanotechnology Materials and Devices Conference (NMDC), 2018, pp. 1–4.

Research

August 9, 2018

Research paper published in the proceedings of 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018, pp. 2313-2318.

Research

June 1, 2018

Research paper published in Advanced Materials Letters, 2018, Volume 9, Issue 6, pp. 444–449.

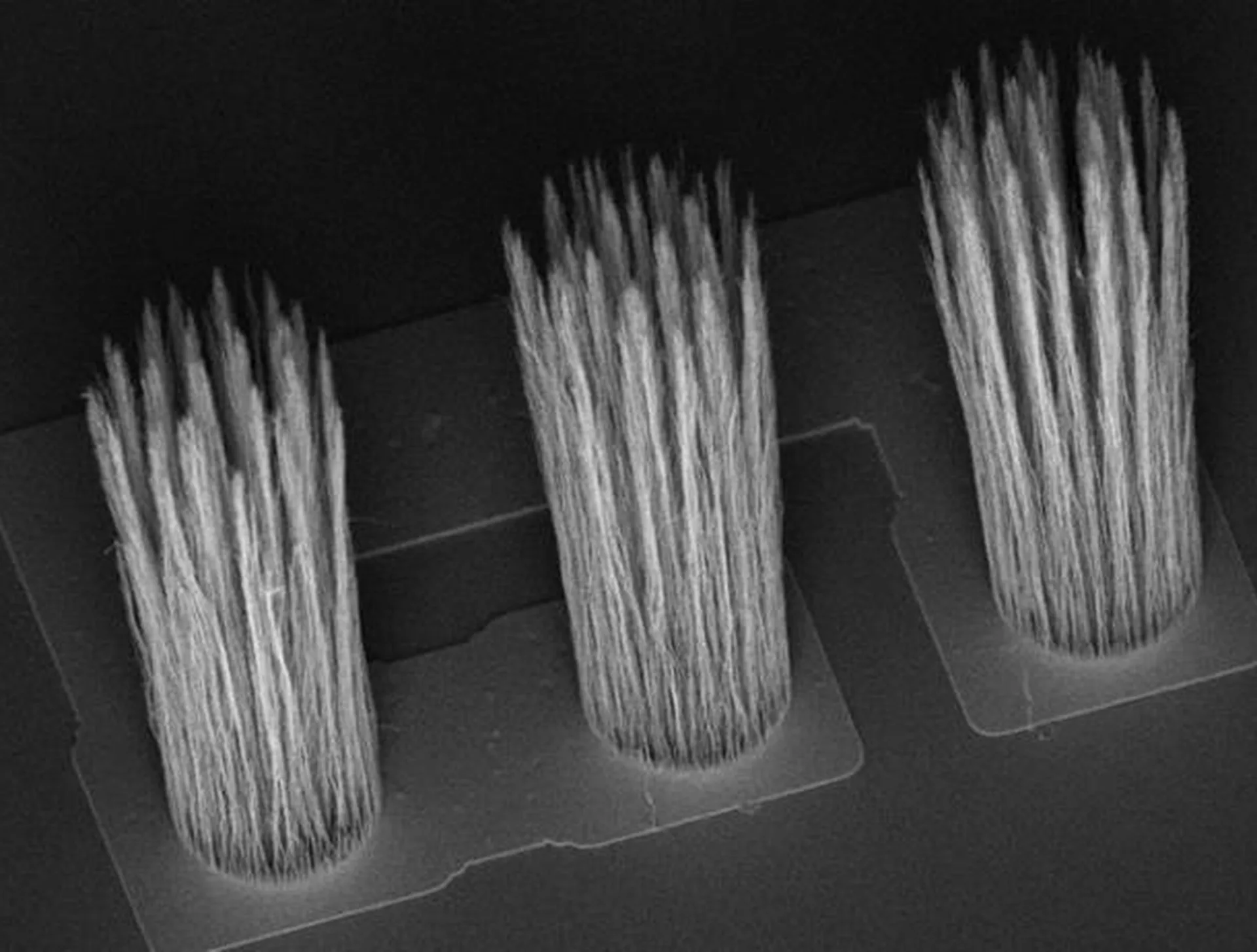

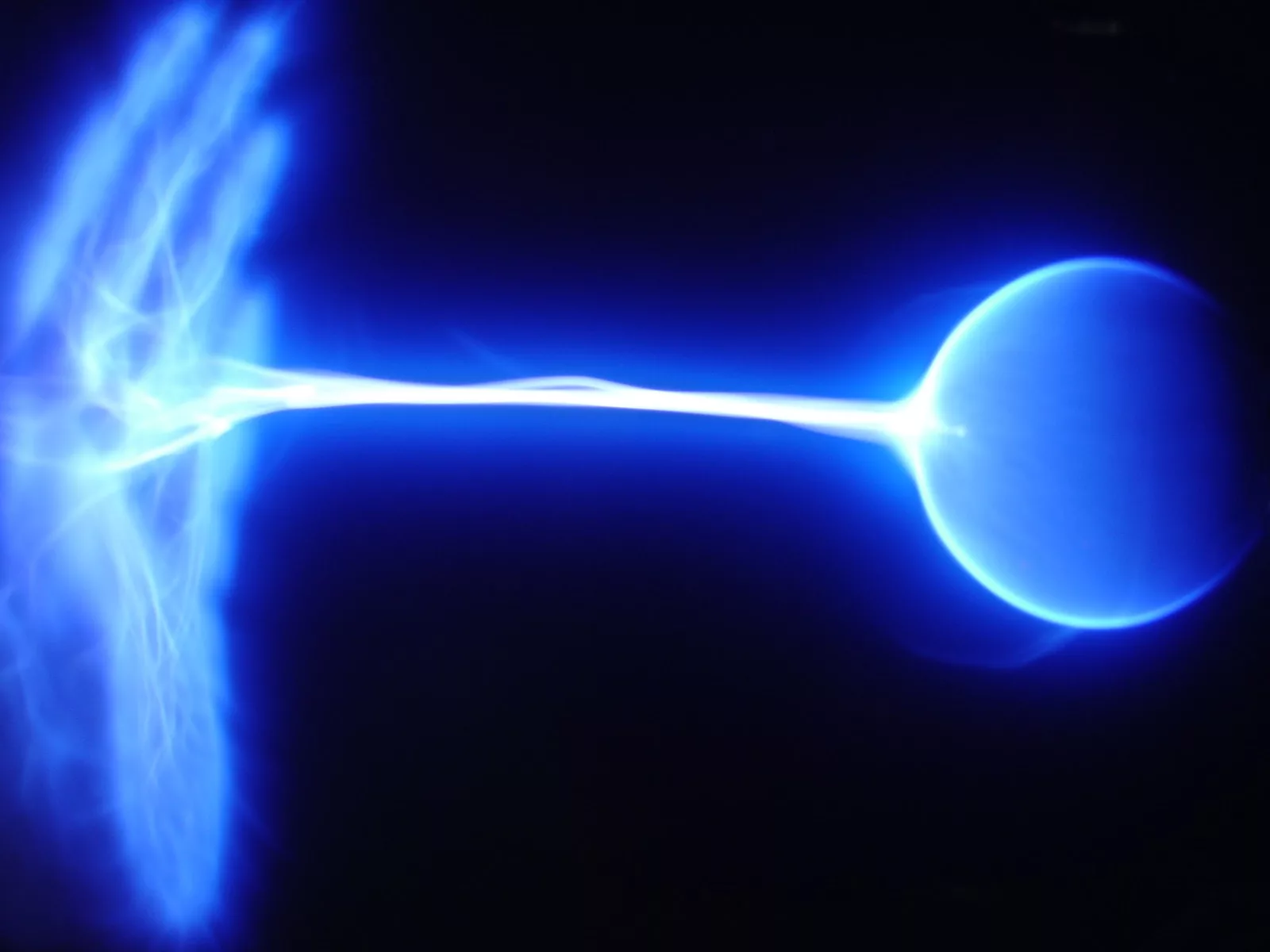

Videos

October 24, 2017

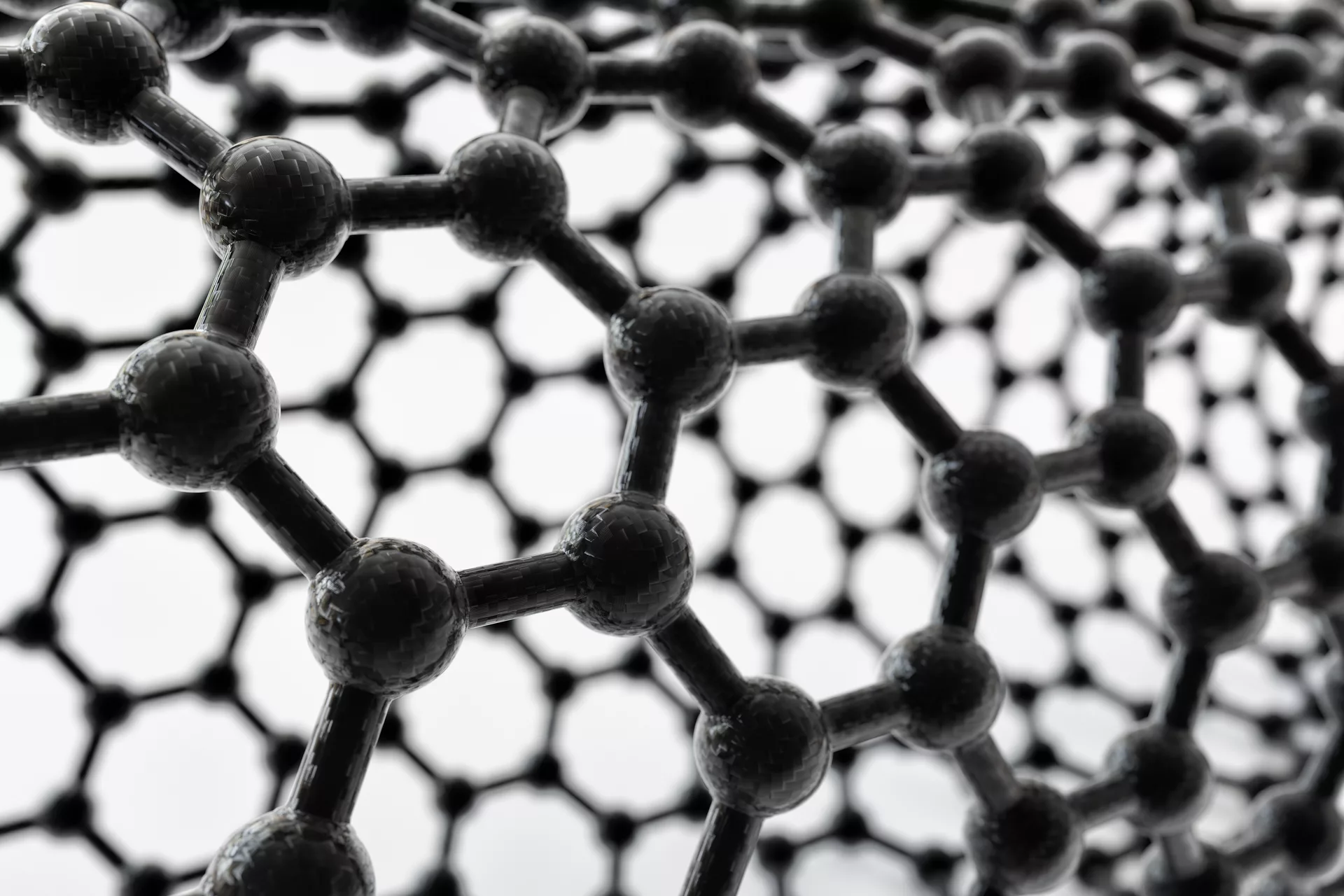

What are carbon nanofibers? How can they be used in the semiconductor industry? What is the role of Smoltek? The answers are given in this short, informative video.

Research

October 16, 2017

Research paper published in Solid–State Electronics, Volume 139, January 2018, pp. 75–79.

Research

August 3, 2017

Research paper published in the proceedings of 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), 2017, pp. 173–178.

Research

July 1, 2017

Article published in Chip Scale Review, Jul–Aug, 2017, pp. 38–40.

Research

June 12, 2017

Research paper published in International Journal of Electrochemical Science, 2017, Volume 12, Issue 7, pp. 6653–6661.

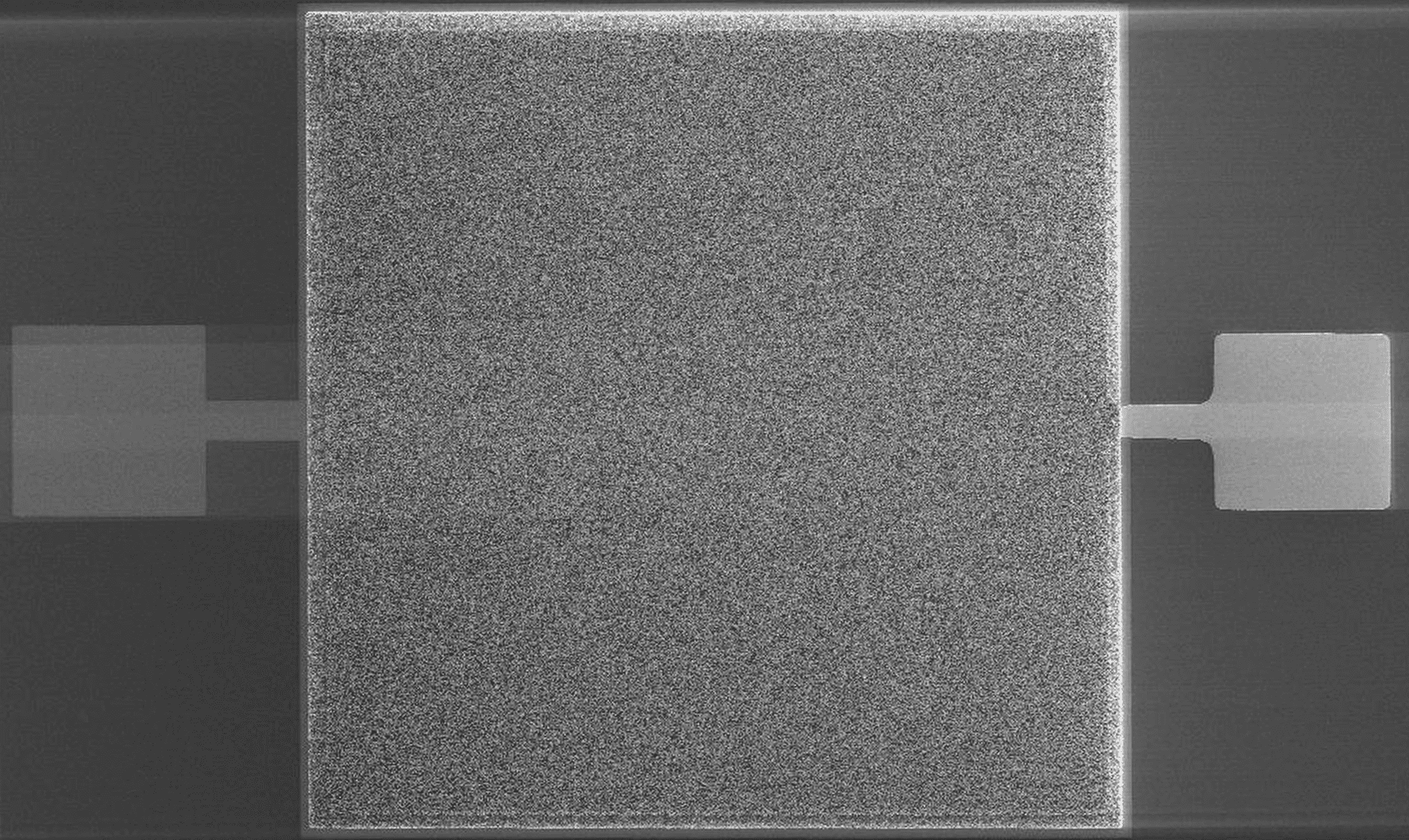

Patents

May 3, 2017

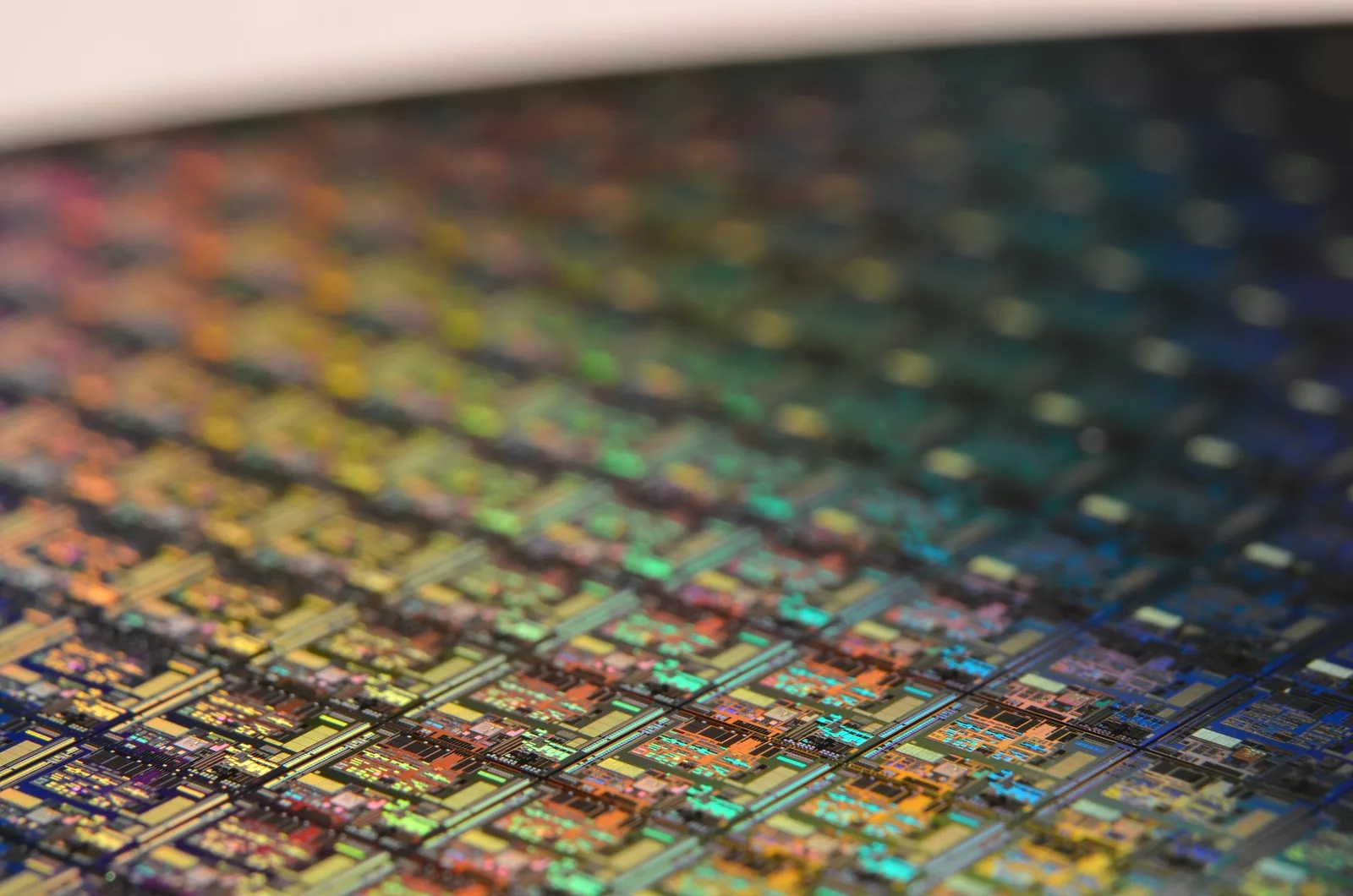

The Assembly platform family is a particular application in the field of interconnects and heterogeneous integration.

Patents

February 24, 2017

The Interposer family is covering Smoltek's CNF-MIM capacitors technology and various use cases for the same, primarily in the field of interposers for advanced packaging and heterogenous integration of semiconductors.

Research

September 29, 2016

Research paper published in Journal of Micromechanics and Microengineering, 2016, Volume 26, Number 12.

Research

August 2, 2016

Research paper published in Journal of Nanomaterials, vol. 2016, Article ID 1537269, 17 pages, 2016.

Research

May 17, 2016

Research paper in the proceedings of Micronano System Workshop MSW 2016, Lund, Sweden, 17–18 May, 2016.

Research

December 1, 2015

Research paper in the proceedings of The 15th International Conference on Micro and Nanotechnology for Power Generation and Energy Conversion Applications (PowerMEMS 2015), Boston, USA, 1–4 December, 2015.

Research

April 6, 2015

Research paper published in IEEE Nanotechnology Magazine, Volume 9, Number 2, June 2015, pp. 33–38.

Research

February 25, 2015

Research paper published in Solid–State Electronics, Volume 107, May 2015, pp. 15–19.

Research

February 25, 2015

Research paper published in Science and Technology of Advanced Materials, 2015, Volume 16, Issue 1.