Sign up for our newsletter!

Your data will be handled in compliance with our privacy policy.

Your data will be handled in compliance with our privacy policy.

The Multilayer Cap patent family introduces a MIM-capacitor device that can double or triple the capacitance density of Smoltek's CNF-MIM capacitors. The patent details an invention for a layered energy storage device, specifically a capacitor, built using a metal-insulator-metal (MIM) configuration.

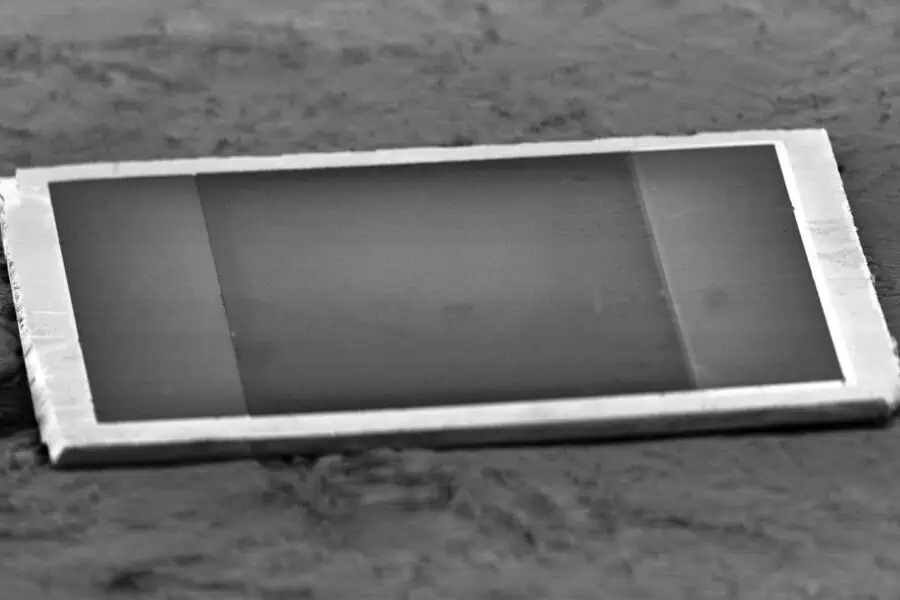

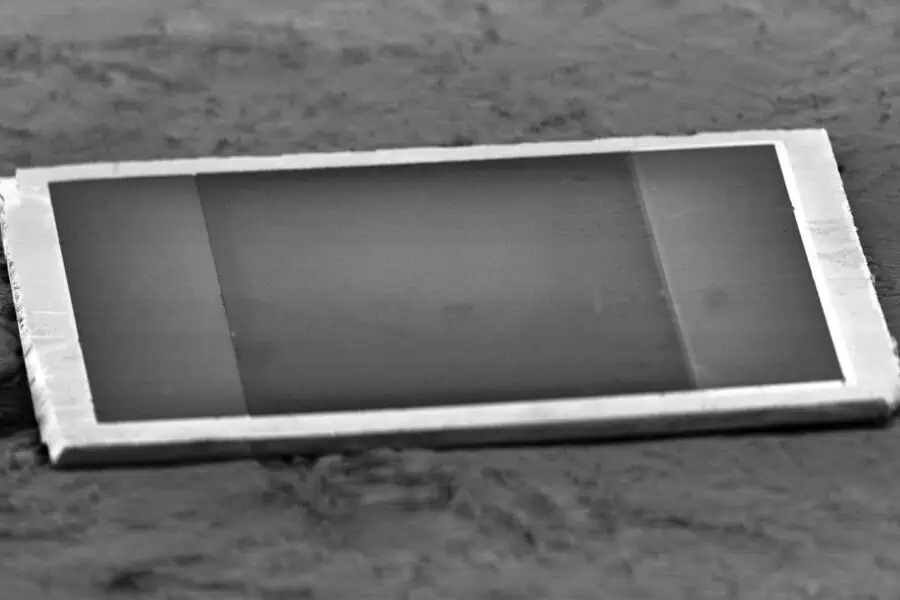

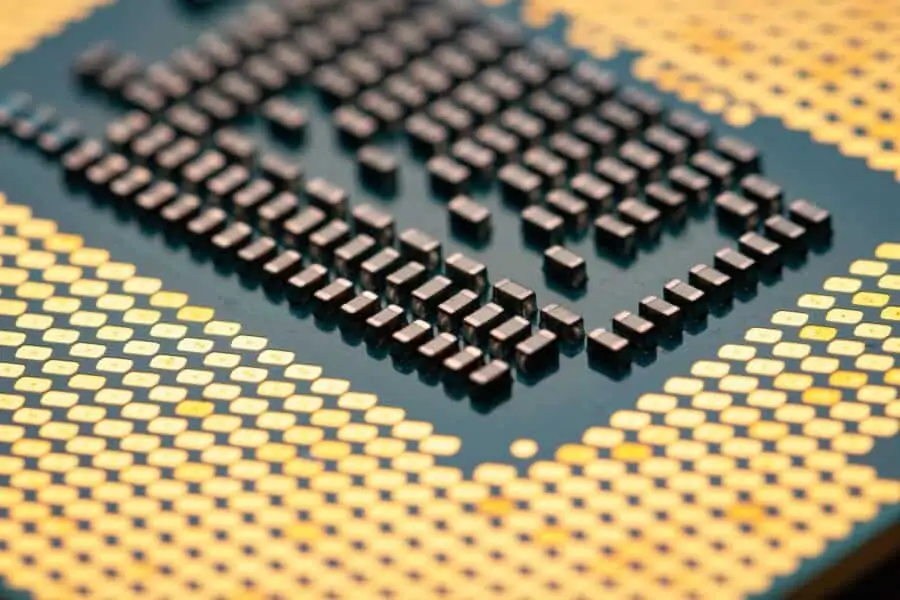

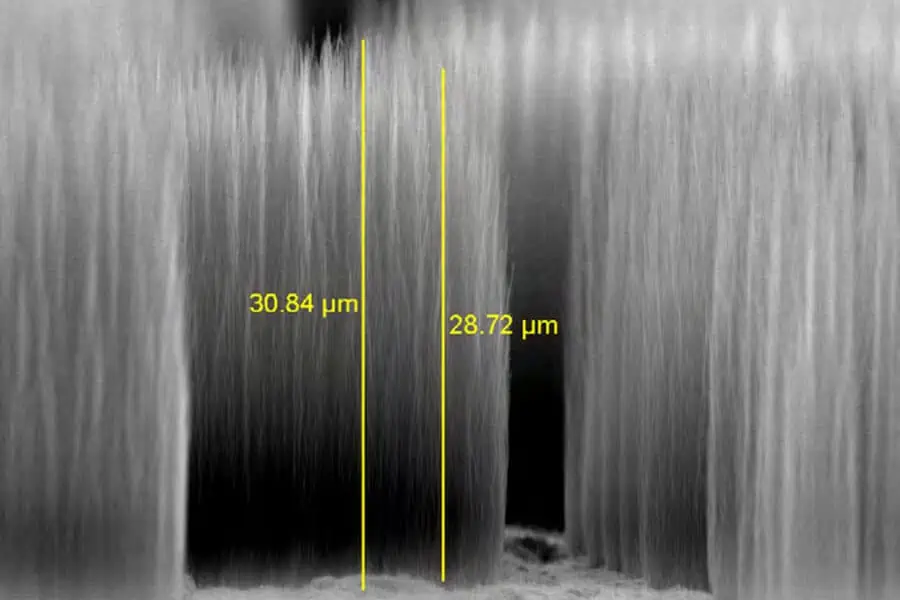

The Discrete CNF-MIM patent family is covering a method for manufacturing of discrete capacitor components based on our CNF-MIM technology. The innovation exploits the extra-ordinary surface to volume ratio provided by carbon nanofibers to create a MIM capacitor with unparalleled high capacitance density.

Research paper published in the proceedings of 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), 2021, pp. 1205-1210.

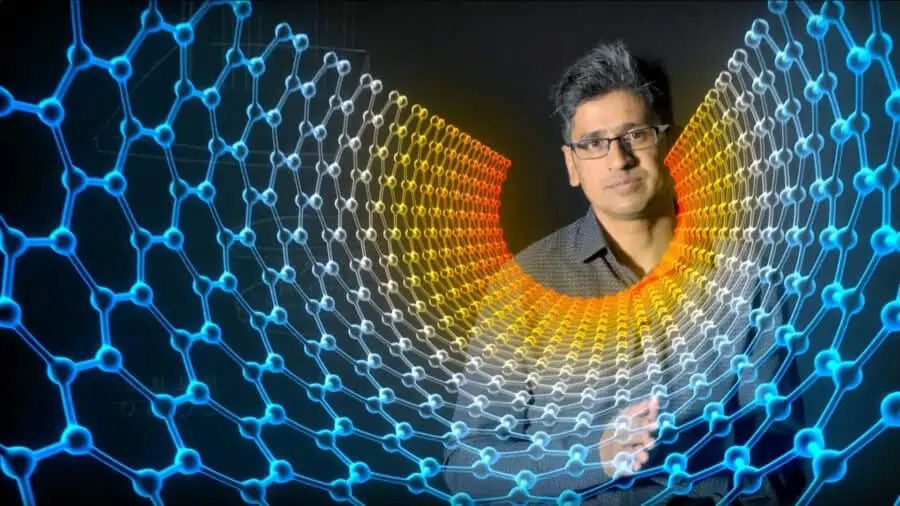

Smoltek's business model and IP strategy for the company's extensive patent portfolio have shifted over the years – from scientific curiosity in the beginning into solving advanced industry needs today. In this video, published in November 2020, Dr Shafiq Kabir, Co-founder and former Chief Innovation Officer (CIO) explains how the IP-strategy has transformed as the company has evolved.

Research paper presented in the proceedings of the 53rd International Symposium on Microelectronics, IMAPS 2020, October 5-8, 2020.

Research paper published in the proceedings of 2020 IEEE 20th International Conference on Nanotechnology (IEEE-NANO), 2020, pp. 213-216.

Research paper published in the proceedings of 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), 2020, pp. 2139-2144.

Research paper published in the proceedings of 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), 2020, pp. 1614-1619.

Research paper published in the proceedings of 2019 Electrical Design of Advanced Packaging and Systems (EDAPS), 2019, pp. 1-3.

Award for best presentation.

Research paper published in the proceedings of 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), 2019, pp. 1870-1876.

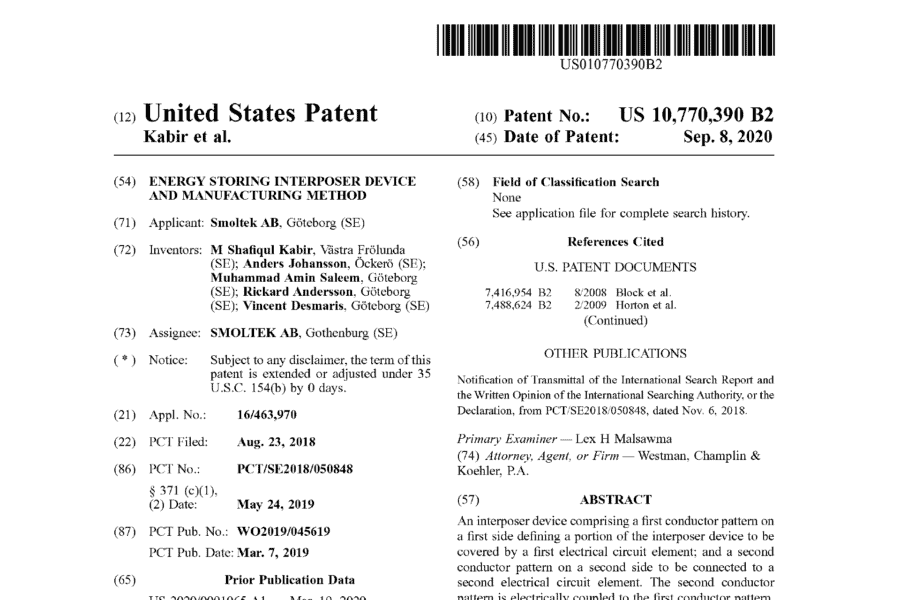

The Compact Energy Storage Interposer family is covering the invention and manufacturing of extremely thin energy storage devices embedded in an interposer.

What are carbon nanofibers? How can they be used in the semiconductor industry? What is the role of Smoltek? The answers are given in this short, informative video.

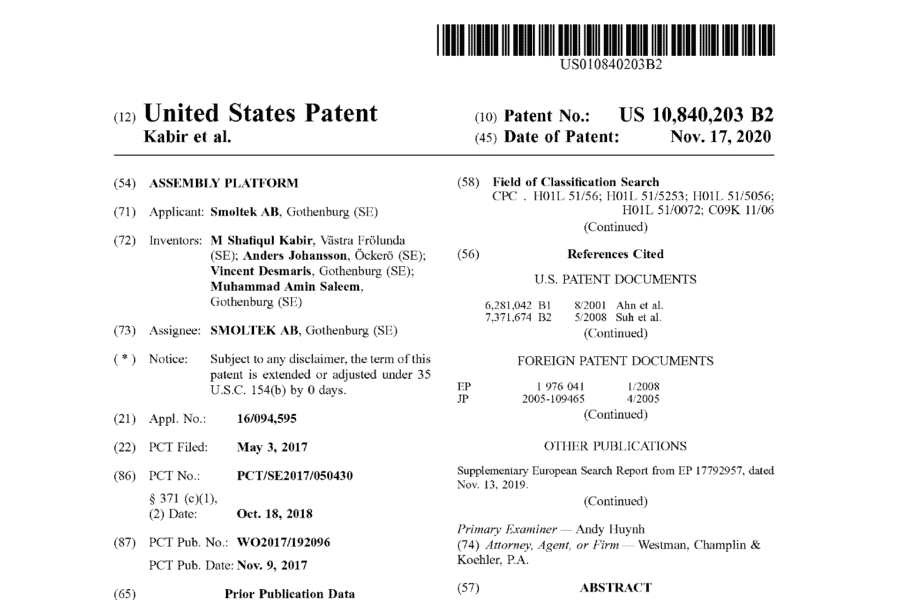

The Assembly platform family is a particular application in the field of interconnects and heterogeneous integration.

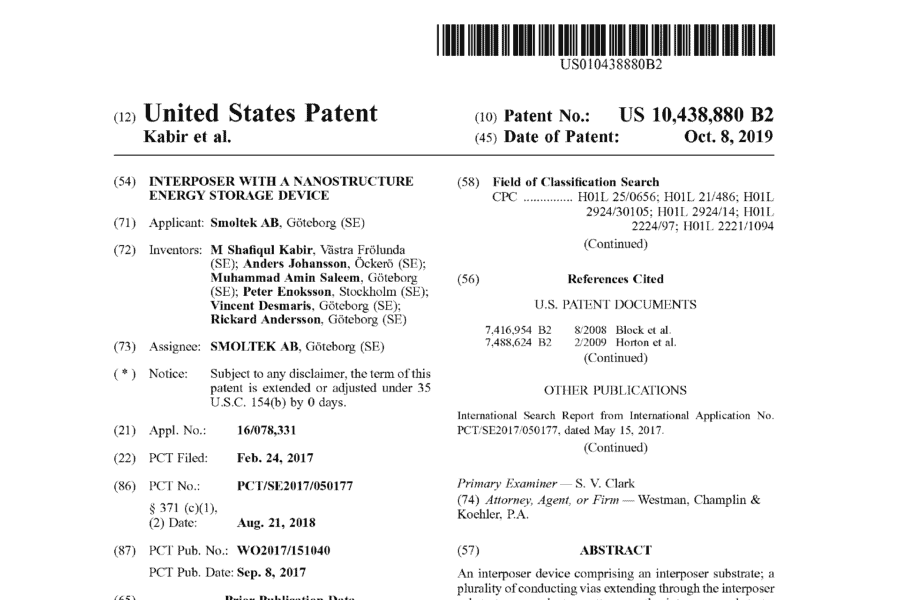

The Interposer family is covering Smoltek's CNF-MIM capacitors technology and various use cases for the same, primarily in the field of interposers for advanced packaging and heterogenous integration of semiconductors.

Research paper in the proceedings of Semicon Taiwan 2014.

Research paper in the proceedings of 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), 2014, pp. 1071–1076.

Research paper published in the IPC APEX EXPO Conference Proceedings, March 23–27, 2014.

Article published in MEPTEC Report, Volume 18, Issue 1.

Research paper in the proceedings of NT11 International Conference on the Science and Application of Nanotubes, University of Cambridge, United Kingdom, July 10–16, 2011.

The Catalyst Diffusion family is covering a method for manufacturing a plurality of nanostructures on a substrate.